Министерство образования и науки Российской Федерации

Федеральное государственное автономное образовательное учреждение

высшего профессионального образования

**«МОСКОВСКИЙ ФИЗИКО-ТЕХНИЧЕСКИЙ ИНСТИТУТ**

(государственный университет)»

Кафедра информатики

*На правах рукописи*

*БИТНЕР Вильгельм Александрович*

**ИССЛЕДОВАНИЕ И РЕАЛИЗАЦИЯ МОДЕЛИ

СТАТИЧЕСКОГО АНАЛИЗА НАХОЖДЕНИЯ СОСТОЯНИЯ ГОНКИ

В МНОГОПОТОЧНЫХ АЛГОРИТМАХ С ИСПОЛЬЗОВАНИЕМ

ЛИНЕАРИЗОВАННОГО ГРАФА ПОТОКА УПРАВЛЕНИЯ**

Специальность: 05.13.11 – Математическое и программное обеспечение

вычислительных машин, комплексов и компьютерных сетей

Диссертация на соискание ученой степени

кандидата технических наук

Научный руководитель:

доктор физико-математических наук, профессор

Тормасов Александр Геннадьевич

# Оглавление

|                                                                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Оглавление .....                                                                                                                                                      | 2  |

| Введение.....                                                                                                                                                         | 4  |

| Актуальность темы .....                                                                                                                                               | 5  |

| Цель работы и задачи исследования .....                                                                                                                               | 6  |

| Объект исследования .....                                                                                                                                             | 7  |

| Предмет исследования.....                                                                                                                                             | 8  |

| Метод исследования .....                                                                                                                                              | 8  |

| Научная новизна.....                                                                                                                                                  | 8  |

| Практическая ценность .....                                                                                                                                           | 9  |

| Публикации и апробация результатов .....                                                                                                                              | 10 |

| Структура и объем диссертации.....                                                                                                                                    | 11 |

| Глава 1. Общие понятия и существующие методы анализа многопоточных алгоритмов для обнаружения состояний гонок .....                                                   | 15 |

| 1.1. Понятие об оптимизации и промежуточном коде .....                                                                                                                | 15 |

| 1.2. Оптимизирующие компиляторы.....                                                                                                                                  | 17 |

| 1.3. Средства статического анализа .....                                                                                                                              | 20 |

| 1.4. Метод статического анализа на основе графа совместного исполнения потоков .....                                                                                  | 26 |

| Глава 2. Реализации модели статического анализа нахождения состояния гонки в многопоточных алгоритмах с использованием линеаризованного графа потока управления ..... | 32 |

| 2.1. Анализ оптимизаций на промежуточном представлении .....                                                                                                          | 32 |

| 2.2. Линеаризация графа потока управления через линейку оптимизаций LLVM .....                                                                                        | 37 |

| 2.3. Анализ инструкций SSA-формы LLVM IR, не влияющих на математическую модель поиска RC.....                                                                         | 41 |

|                                                                                                                                           |    |

|-------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.4. Получения сокращенного оптимизированного промежуточного представления LLVM – Reduced Opt LLVM IR.....                                | 46 |

| 2.5. Контекстно-зависимая линеаризация графа потока управления на сокращенном промежуточном представлении программы.....                  | 51 |

| 2.6. Поиск состояний гонок в исследуемом методе на Reduced CFG .....                                                                      | 54 |

| 2.7. Модель автоматизация поиска состояний гонок.....                                                                                     | 59 |

| Глава 3. Практические результаты и анализ применения программной реализации модели поиска состояний гонок в многопоточных алгоритмах..... | 62 |

| 3.1. Спинлок (спин-блокировка) .....                                                                                                      | 62 |

| 3.2. Некорректный алгоритм спин-блокировки .....                                                                                          | 67 |

| 3.3. Алгоритм Петерсона .....                                                                                                             | 69 |

| 3.4. Стек Трейбера .....                                                                                                                  | 70 |

| 3.5. Выводы .....                                                                                                                         | 84 |

| Заключение .....                                                                                                                          | 85 |

| Список использованных источников .....                                                                                                    | 87 |

| Приложение .....                                                                                                                          | 92 |

## **Введение**

Современная тенденция развития микропроцессоров и вычислительного оборудования обуславливает создание новых подходов к промышленной разработке программного обеспечения, отвечая все более высоким требованиям потребителя и современным условиям конкуренции. В частности, повышение количества ядер в микропроцессорах заставляет программных разработчиков использовать многопоточные алгоритмы и применять технологии многопоточной программной разработки не только для высокопроизводительных систем, но и для персональных компьютеров и мобильных устройств [2, 30].

Повышение количества ядер в микропроцессорах зачастую сопровождается понижением тактовой частоты каждого ядра микропроцессора, что усугубляет положение ранее написанных однопоточных программ. Далеко не редкость в современной ИТ-индустрии ухудшение производительности промышленных комплексов программ при переходе на более современные вычислительные системы с новыми поколениями микропроцессоров. Данный факт дополнительно стимулирует разработку многопоточных программ для достижения наилучших показателей производительности.

Разработка многопоточных программ с наилучшими показателями производительности не имеет общего подхода. Каждый случай индивидуален в зависимости от архитектуры вычислительной системы и сложности комплексов программ. Такое положение приводит к появлению трудно выявляемых ошибок в коде программ, особенно связанных с параллельным исполнением потоков. Таким образом, всегда остается актуальным разработка новых и совершенствование старых средств верификации и контроля качества программ во время разработки программного обеспечения (ПО).

## **Актуальность темы**

Среди наиболее сложных для обнаружения ошибок в многопоточных программах являются состояния конкурентного доступа к памяти или состояния гонки (*race condition*, *RC*). *Race condition* – ситуация, когда несколько потоков одновременно обращаются к одному и тому же ресурсу, причем хотя бы один из потоков выполняет операцию записи, и порядок этих обращений точно не определен [5]. Наличие состояний гонок приводит к недетерминированному поведению программы.

Методики поиска состояний гонок обычно разделяют на *статический анализ, динамический анализ, проверку на основе моделей и аналитического доказательства корректности программ*. Динамический анализ посвящен анализу эмпирических запусков программы на определенном наборе тестов и входных данных. Существуют довольно много коммерческих и бесплатных программных утилит, которые позволяют проводить динамический анализ на разных платформах и архитектурах: Intel Thread Checker, CHESS и т.д. Недостатком данного вида анализа является невозможность анализа больших программных систем, т.к. количество необходимых тестов экспоненциально растет в зависимости от количества входных параметров.

Статический анализ – это анализ без исполнения программы. Преимуществом данного вида анализа является возможность проверки и устранения ошибок в коде во время разработки, глубина анализа как правило выше, что позволяет гарантировать более высокую надёжность конечного программного продукта. В качестве недостатка статического анализа можно выделить сложность применения в промышленных масштабах и не самую лучшую надежность методов анализа, которые не давали бы ложные срабатывания: обнаружение состояний гонок, когда их на самом деле нет, либо упущение реально присутствующих состояний гонок.

В рамках диссертационной работы за основу взята математическая модель статического анализа многопоточных программ, описанных в исследованиях А.Г. Тормасова, М.Ю. Кудрина, А.С. Прокопенко, Н.В. Зaborовского [13-15]. Математическая модель строится на основе анализа графа совместного исполнения потоков, построенного по определённым участкам кода программы. Результаты исследований зарекомендовали себя как перспективный и эффективный метод поиска потенциальных угроз состояния гонки. Однако представленный метод хорошо работает на линейных участках и имеет ряд ограничений при анализе более сложных конструкций кода, таких как циклы, условные конструкции, алиасы. Реализация и исследование математической модели для применения в промышленных комплексах программ остается актуальной задачей, в рамках которой необходимо разрешить ограничения представленного метода и, как следствие, расширить класс применимости метода среди промышленного ПО.

## **Цель работы и задачи исследования**

В рамках работы [13] уже была предпринята попытка приблизить математическую модель к промышленному использованию метода анализа. Однако реализация и соответствующая математическая модель, выполненная с использованием высокоуровневого промежуточного представления не поддерживаемой системы и не имеющая широкого использования, не позволяет применять метод в промышленной разработке ПО. С другой стороны, современная промышленная разработка ПО не обходится без использования оптимизирующих компиляторов, которые используют промежуточное представление программы (intermediate representation – IR) для проведения оптимизаций над кодом программы. Таким образом, использование IR промышленного компилятора в качестве основы для проведения анализа позволило бы значительно улучшить применимость представленного метода.

Существенную роль в методе может сыграть оптимизации компиляторов, которые могли бы создать наилучший контекст IR перед применением метода анализа многопоточных программ.

**Целью диссертационной работы является исследование, адаптация и реализация математической модели статического анализа многопоточных программ.**

Для достижения поставленной цели в работе решаются следующие основные задачи:

- Исследование и анализ современных оптимизирующих компиляторов и их оптимизаций. Выявление наиболее подходящих оптимизаций для создания такого контекста IR, который содержал бы наименьшее количество изменений потока управления, т.е. циклов и условных конструкций.

- Разработка дополнительных оптимизаций над графом потока управления, не влияющих на анализ контекста программы в исследуемом методе статического анализа.

- Адаптация математической модели и метода анализа под новый контекст IR.

- Реализация математической модели в контексте промышленного IR в виде автоматизированной системы обнаружения состояний гонок в программе.

## **Объект исследования**

В работе объектом исследования является процедура поиска состояний гонок в многопоточных алгоритмах, а также оптимизация анализируемого контекста на промежуточном представлении с помощью математической модели, основанная на графах совместного исполнения потоков.

## **Предмет исследования**

В работе предметом исследования является математическая модель, основанная на графах совместного исполнения потоков, построение которых осуществляется по коду программ на языках Си и Си++.

## **Метод исследования**

В работе применяются и используются методы теории множеств, теории графов, теории компиляции, методы программирования на языках высокого уровня.

## **Научная новизна**

В процессе исследования получены следующие новые научные результаты, выносимые на защиту:

- Программная реализация системы обнаружения состояния гонок в многопоточных алгоритмах на основе IR промышленного компилятора, которая позволяет получать IR программ различных языков высокого уровня, разных платформ и архитектур. Использование общепризнанного и популярного компилятора гарантирует применимость метода к широкому классу задач на долгие годы вперед. Возможность получения унифицированного IR программ, ориентированных на такие архитектуры, как Intel, ARM, Power, позволяет значительно расширить класс применимости метода в среде коммерческого ПО. Появилась возможность анализировать код программы на предмет состояния гонок на разных этапах компиляции – до применения оптимизаций и после применения оптимизаций, что дает дополнительную возможность проверки.

- Математическая модель, адаптированная под контекст нового IR.

- Метод линеаризации графа потока управления для представленного анализа. Особенность представленного метода статического анализа позволил создать дополнительную оптимизацию графа потока управления, с помощью которой удалось в некоторых случаях избавиться от лишних узлов графа потока управления и, как следствие, уменьшить количество ветвления управления на графике.

- Комплекс программ и результаты вычислительных экспериментов для выявления наличия гонок в некоторых многопоточных алгоритмах, в том числе неблокирующих.

Работа имеет принципиальную новизну, как в постановке задачи, так и в выборе методов решения поставленных задач.

## **Практическая ценность**

Усовершенствована методика нахождения состояний гонок в многопоточных алгоритмах, реализация которых используется в коммерческом ПО. Разработанные программные модули позволили сделать методику нахождения состояний гонок в промышленном ПО более автоматизированной, надежной и универсальной, что было достигнуто благодаря использованию промежуточного представления оптимизирующего компилятора LLVM.

Выявленные и предложенные оптимизации LLVM позволили получать наиболее подходящий контекст для применения анализа с точки зрения производительности поиска состояний гонок в алгоритме.

Предложенная методика линеаризации графа потока управления, которая используется после оптимизаций LLVM и перед основным анализом, позволила расширить класс задач, пригодных для анализа на предмет наличия состояний гонок исследуемого метода.

Таким образом, программная реализация новшеств и улучшений позволила расширить класс задач, для которых применим метод статического анализа на

основе графа совместного исполнения потоков. Как следствие, данный метод анализа состояний гонок можно более широко использовать для верификации промышленного ПО.

## **Публикации и апробация результатов**

По теме диссертации опубликовано 9 печатных работ, в том числе 3 в рецензируемых изданиях, рекомендованных ВАК РФ для опубликования основных научных результатов диссертаций.

Публикации в ведущих рецензируемых журналах, входящие в перечень ВАК:

1. Битнер В.А., Тормасов А.Г. Анализ и сокращение промежуточного представления программы в модели статического анализа нахождения состояния гонки в многопоточных алгоритмах // Вестник КГТУ им. А.Н. Туполева, 2014. – №3. – С. 203-212.

2. Битнер В.А., Тимербаев Н.Ф. Контекстно зависимая линеаризация графа потока управления в статическом анализе состояний гонок в многопоточных алгоритмах // Вестник Казанского технологического университета, 2014. – Т. 17, №15. – С. 187-192.

3. Битнер В.А., Зaborовский Н.В. Построение универсального линеаризованного графа потока управления для использования в статическом анализе кода алгоритмов // Моделирование и анализ информационных систем, 2013. – Т. 20, №2. – С. 166-177.

Результаты работ докладывались автором на научных конференциях и семинарах:

1. Труды 57-й научной конференции МФТИ «Актуальные проблемы фундаментальных и прикладных наук в современном информационном обществе» (Москва, 2014).

2. Научная конференция «Математическое моделирование и информатика» при ФГБОУ ВПО МГТУ «СТАНКИН» (Москва, 2014).

3. The 8th Congress of the International Society for Analysis, its Applications, and Computation (Москва, 2011).

4. Международной заочной научно-практической конференции «Актуальные проблемы науки» (Тамбов, 2011).

5. Труды 52-й научной конференции МФТИ «Современные проблемы фундаментальных и прикладных наук» (Москва, 2009).

6. XXXVI международная молодежная научная конференция «Гагаринские чтения» (Москва, 2009).

## **Структура и объем диссертации**

Диссертационная работа состоит из введения, трех глав, заключения, одного приложения и списка использованных источников. Список использованных источников включает 37 наименований. Общий объем работы составляет 103 страницы. Объем приложений составляет 12 страниц.

Во **введении** обоснована актуальность темы, сформулирована цель работы и определен перечень решаемых задач, указана новизна научных изысканий, отмечены особенности подхода, раскрываемого в диссертационной работе, практическая ценность полученных решений и разработок, а также дан краткий обзор содержания по главам.

В **первой главе** даются необходимые определения и понятия, которыми оперируют в работе. В данной главе приводится аналитический обзор программных разработок и литературы по теме диссертации. Проведен анализ оптимизирующих компиляторов и типов промежуточных представлений, который позволил сформулировать подход к разработке программных модулей для имплементации метода анализа состояний гонок на основе графа совместного исполнения потоков.

В первой главе при анализе оптимизирующих компиляторов делается вывод о возможности использовать и адаптировать некоторые оптимизации компилятора с целью получения наиболее удобного и эффективного представления программ, написанных на языке высокого уровня, что позволит решить задачу линеаризации CFG для повышения эффективности и расширения применимости исследуемого метода статического анализа многопоточных алгоритмов на предмет состояния гонки.

Помимо анализа оптимизирующих компиляторов в первой главе приводится обзор существующих средств поиска состояний гонок в программах. Уделяется внимание слабым и сильным качествам тех или иных подходов и технологий. Делается вывод о текущем положении статических анализаторов, что на практике они дают неточный ответ о наличии того или иного свойства в программе. Основной принцип статического анализа: либо точность, либо время. Выбор оптимального сочетания времени работы анализатора и точности является практической задачей, которая разрешается в каждом случае отдельно.

В первой главе приводится описание исследуемой математической модели поиска состояний гонок в многопоточных алгоритмах, а также вводятся необходимые определения и понятия, связанные с исследуемой моделью.

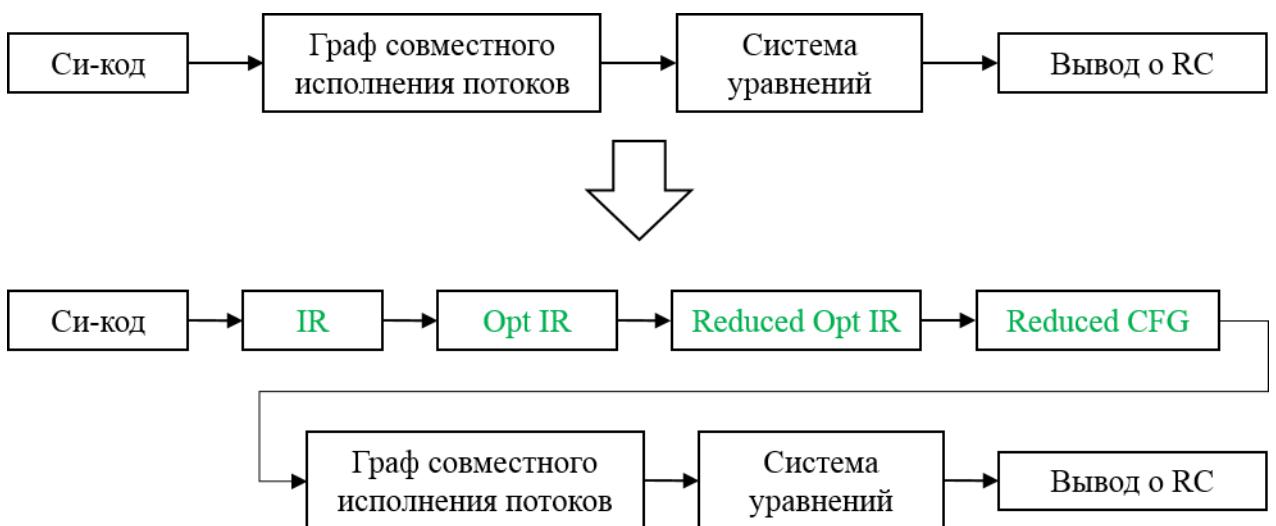

Во **второй главе** описывается реализация модели статического анализа нахождения состояния гонки в многопоточных алгоритмах с использованием линеаризованного графа потока управления. В данной главе проводится анализ оптимизаций компилятора LLVM. LLVM содержит более 100 уникальных оптимизаций, которые были проанализированы с точки зрения влияния на CFG. Также в главе рассматривается подход использования выявленных оптимизаций LLVM на практике с целью линеаризации графа потока управления.

Во второй главе проводится анализ инструкций LLVM IR, не влияющих на математическую модель поиска состояний гонок, и соответствующее доказательство их корректного удаления из анализируемого контекста программы, что приводится в утверждениях и теоремах 1-3. Как следствие, в

данной главе приводится описание метода получения сокращенного промежуточного представления программы, удаляя ненужные инструкции из контекста.

В последующем в данной главе на основе доказанных теорем и утверждений приводится описание алгоритма удаления пустых CFG-узлов, полученных на сокращенном промежуточном представлении. Описанный алгоритм используется в общей модели получения контекстно-зависимого линеаризованного графа потока управления. На основе приведенной модели приводится описание организации поиска состояния гонок на основе исследуемого метода статического анализа и линеаризованного графа потока управления.

В заключительной части второй главы приводится описание программного комплекса, разработанного в рамках данной работы, для организации с высокой степенью автоматизации систему поиска неразрешимых состояний гонок. Приводится описание архитектуры системы поиска и описание составных частей разработанного программного комплекса.

В **третьей главе** описывается практическое применения реализованного комплекса программ на различных алгоритмах. Показывается, что на модельных задачах получаются верные результаты и демонстрируется корректность подхода, используя промежуточное представление программы и его дальнейшее упрощение.

В третьей главе приводятся программный код, подробные результаты процесса получения Reduced CFG, а также результаты анализа Reduced CFG в Wolfram Mathematica. По результатам применения прототипа комплекса программ делается заключение, что подход работает корректно на модельных задачах и может быть использован в других реальных задачах с двумя потоками, компилируемых оптимизирующим компилятором CLANG&LLVM.

В **приложении** подробно иллюстрируется работа предложенной модели организации поиска состояния гонок. Приводятся промежуточные

анализируемые графы, полученные анализатором на Wolfram Mathematica, такие как классы эквивалентности на графе совместного исполнения потоков, анализ путей на расчетном графе. Приведенные данные в приложении являются дополнением к третьей главе, где приводятся практические результаты анализа различных многопоточных алгоритмов

В **заключении** сформулированы основные результаты диссертационной работы. Результаты и положения, выносимые на защиту, совпадают.

# **Глава 1. Общие понятия и существующие методы анализа многопоточных алгоритмов для обнаружения состояний гонок**

## **1.1. Понятие об оптимизации и промежуточном коде**

Введем понятие оптимизации, которое будет использоваться в дальнейшем. *Оптимизация* – это эквивалентное преобразование над промежуточным представлением компилятора.

*Промежуточное представление* – структура данных, фиксирующая состояние(я) программы в процессе компиляции от исходной записи на входном языке до выходного состояния – целевого исходного кода программы, исполняемой на заданной платформе. Основные функции промежуточного представления:

- отображение и сохранение инвариантной семантики исходной программы;

- базис для проведения анализа и оптимизирующих преобразований программы;

- интерфейс взаимодействия со всеми фазами компиляции, позволяющий фиксировать и передавать изменения программы.

В процессе трансляции компилятор часто использует промежуточное представление исходной программы, предназначенное, прежде всего, для удобства генерации кода и/или проведения различных оптимизаций. Сама форма промежуточного представления зависит от целей его использования. Наиболее часто используемыми формами промежуточного представления являются ориентированный граф (в частности, абстрактное синтаксическое дерево, в том числе атрибутированное), трехадресный код (в виде троек или четверок), префиксная и постфиксная запись.

*Линейным участком* в промежуточном представлении будем называть совокупность операций с выделенными входной и выходной операциями,

передача управления в который может происходить только через входную операцию.

*Граф потока управления* [16, 25] – аналитическая структура, которую логически можно представить, как управляющую надстройку над промежуточным представлением. В реализации наиболее распространенной схемой является представление управляющего графа как отдельного объекта, имеющего взаимно однозначное соответствие с операционной семантикой промежуточного представления, в которой выражена вся полнота семантики передачи управления. Представляет собой направленный связный граф, каждый узел (вершина) которого соответствует линейному участку, а дугам – управляющие связи между ними, отображающие передачу управления. В графе есть два выделенных узла: узел START, не имеющий входных дуг, и узел STOP, не имеющий выходных дуг. Для простоты обозначения граф управления называют CFG (Control Flow Graph), а узлы и дуги графа управления – CFG-узлы и CFG-дуги, соответственно. Далее в тексте будут синонимично употребляться оба обозначения графа управления и его составляющих.

Как правило, для любой оптимизации можно выделить объект применения. *Объект применения* – это некоторое подмножество промежуточного представления, с которым работает оптимизация. Например, операция, пара операций, узел управляющего графа, цикл, процедура. Оптимизации на уровне операций принято называть низкоуровневыми оптимизациями, оптимизации, работающие на уровне узлов управляющего графа – макрооптимизациями.

Цели оптимизации можно подразделить на две категории. Первая цель состоит в том, чтобы избавиться от лишних вычислений, вторая – наиболее оптимально адаптировать программу к имеющимся архитектурным особенностям и аппаратным ресурсам. При этом обе цели не являются полностью независимыми. Иногда адаптация к аппаратным особенностям требует увеличить число выполняемых команд, чтобы сократить общее время их

выполнения, но это возможно только при наличии параллельных аппаратных ресурсов.

Программа, поступающая на вход оптимизирующего компилятора, предварительно преобразуется в вид, удобный для анализа и оптимизаций. Далее для нее строятся специальные вспомогательные структуры данных, облегчающие оба процесса. При анализе компилятор должен найти и устраниить ложные зависимости, для чего зачастую используется техника переименования регистров, а при оптимизации должен избавиться от лишних вычислений, найти наиболее часто выполняемые последовательности команд, опираясь на профильную информацию, и построить для них оптимальный код, включая планирование для архитектур с параллельными исполняющими устройствами.

В данной работе будет уделено большое внимание именно к CFG и связанным с его преобразованием оптимизациям, хотя подобные аналитические структуры, как CFG, далеко не единственны в оптимизирующих компиляторах. При этом промежуточное представление исходной программы можно рассматривать как программу для абстрактной машины, поскольку оно основано на ассемблере целевой архитектуры, но при этом не является программой на языке ассемблера [6]. Данная особенность позволяет наиболее точно и оптимально по сложности использовать промежуточное представление в методе статического анализа состояний гонок в многопоточных алгоритмах, описанном в работах [13-14].

## 1.2. Оптимизирующие компиляторы

Оптимизирующие компиляторы занимают важную роль в современной промышленной разработке, позволяя максимально эффективно использовать аппаратные особенности платформ и архитектур, на которых предполагается исполнение программ. Разработкой собственных оптимизирующих компиляторов занимаются все ведущие ИТ-корпорации и компании, которые

связаны не только с инженерным развитием платформ и архитектур, но и программной разработкой. Основная мотивация к разработке собственного оптимизирующего компилятора – собственными силами эффективнее разрешить проблемы генерации высокопроизводительного и надежного целевого кода отдельно взятой архитектуры. Таким образом, на сегодняшний день существует достаточной обширный пласт коммерческих оптимизирующих компиляторов таких компаний, как Intel, Sun Microsystems, Transmeta, Microsoft, IBM, HP, Elbrus [9].

Помимо коммерческих оптимизирующих компиляторов существуют также бесплатные компиляторы с открытым кодом, которые развиваются группами разработчиков повсеместно во всем мире. Наиболее популярные и зарекомендовавшие себя оптимизирующие компиляторы – это GCC и CLANG&LLVM.

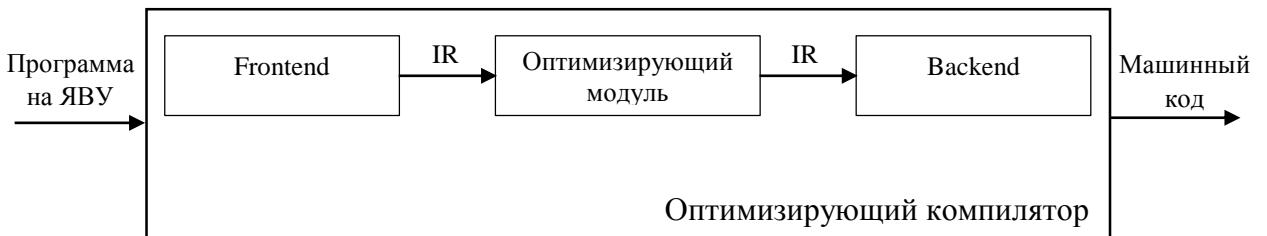

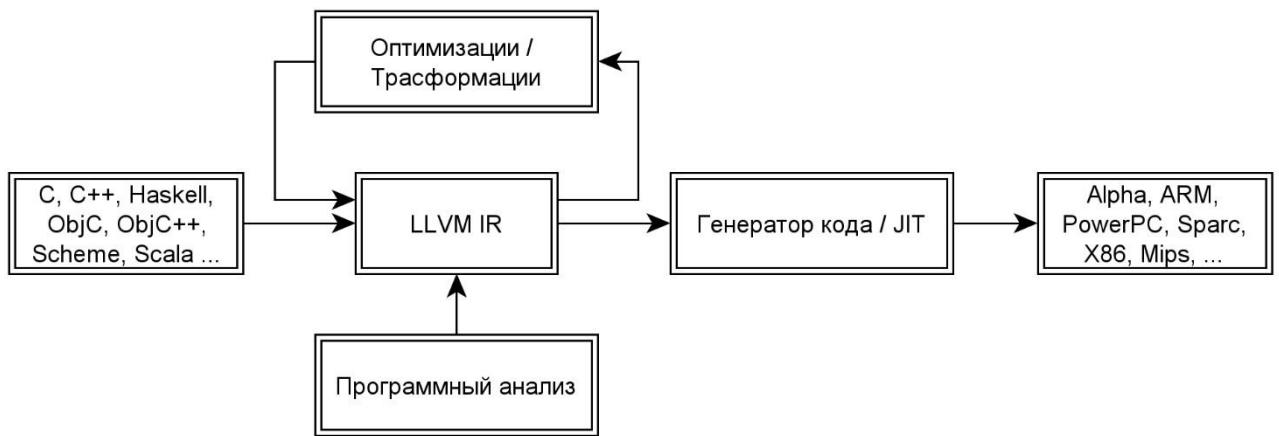

Рис. 1. Структура оптимизирующего компилятора.

Несмотря на богатое разнообразие оптимизирующих компиляторов, их структура состоит из трех абстрактных модулей (см. рис.1): «frontend» – преобразование программы, написанной на языке высокого уровня (ЯВУ), в промежуточное представление (IR – intermediate representation); «оптимизирующий модуль» – процесс анализа и оптимизации промежуточного представления программы; «backend» – генерирование оптимизированного машинного кода.

Помимо общей структуры оптимизирующих компиляторов всегда можно выявить базовые оптимизации, которые имплементированы во всех компиляторах, особенно связанные с анализом и изменением CFG, такие как

оптимизация переходов, оптимизации вызовов оптимизация циклов и цепочек переходов и т.д. [16]. Таким образом, задача линеаризации CFG для организации более эффективного статического анализа алгоритмов в рамках данной работы имеет пересечения с задачами оптимизирующих компиляторов – получения эффективного кода целевой архитектуры. При этом под *линеаризацией CFG* будем понимать процесс уменьшения количества условных переходов в графе потока управления, которые приводят к параллельным веткам исполнения кода в зависимости от условий.

Особенно факт пересечения задач компилятора и линеаризации CFG проявляется для оптимизирующих компиляторов архитектурных платформ, использующих статический подход к распараллеливанию на уровне инструкций – EPIC-архитектуры (Explicitly Parallel Instruction Computing), а также архитектурных платформ с явной поддержкой параллелизма на уровне отдельных инструкций с широким командным словом – VLIW-архитектуры (Very Long Instruction Word).

EPIC- и VLIW-архитектуры, как правило, имеют длинный конвейер, из-за чего остро стоит проблема условных переходов, т.к. в момент исполнения операций условного перехода процессору неизвестно до конца, какая из веток условного перехода будет исполняться. В зависимости от успешности предсказаний условного перехода процессор либо исполняет ранее подкаченные инструкции из конвейера, либо освобождает конвейер и загружает нужные инструкции, что, очевидно, негативно сказывается на производительности исполнения программ. Для решения данной проблемы немалый вклад вносит оптимизирующий компилятор той или иной платформы, который осуществляет различные оптимизации на промежуточном представлении программ в процессе их компиляции.

Процесс оптимизации промежуточного представления компилятора разделен на фазы оптимизации, где каждая фаза реализует отдельную чаще независимую оптимизацию над IR [16]. Все фазы оптимизации формируют

линейку оптимизаций, которая в зависимости от реализации компилятора может меняться по контексту IR либо по требованию пользователя. Особенность реализации компиляторов позволяет получать IR практически после каждой фазы оптимизации, а также соответствующие абстрактные представления этого IR, такие как CFG.

Таким образом, есть возможность использовать и адаптировать некоторые оптимизации компилятора с целью получения наиболее удобного и эффективного представления программ, написанных на языке высокого уровня, что позволит решить задачу линеаризации CFG для повышения эффективности и расширения применимости исследуемого метода статического анализа многопоточных алгоритмов на предмет состояния гонки.

### **1.3. Средства статического анализа**

На сегодняшний день для применения в промышленной разработке программного обеспечения существуют как коммерческие, так и бесплатные статические анализаторы. Фундаментальные подходы в реализации статических анализаторов многопоточных алгоритмов могут быть классифицированы следующим образом [13, 14]:

#### *1. Идентификация ресурсов.*

В анализе требуется определить, какая память разделяется между потоками. В общем случае задачу решить нельзя, потому что адресация памяти может происходить неявно. В случае создания тредов в Unix-системах необходимо добавлять в анализ все глобальные переменные, т.к. автоматически начинают разделяться после создания. Помимо прочего переменные могут передаваться в качестве параметра в поток, причем по указателю или по ссылке, что создает угрозу появления состояний гонок, поэтому такие переменные должны быть также добавлены в анализ.

#### *2. Идентификация потоков.*

Анализ требует идентификации конкурирующих потоков. Такая задача сводится к определению момента создания потоков для каждого языка высокого уровня. Методы создания могут быть как явными – системный вызов (`fork()` в Linux), так и неявными – сигналы и сообщения, при этом создание потока определяется языком программирования, на котором написан анализируемый код программы. Идентифицировать создание потоков можно на стадии компиляции программы.

### *3. Использование псевдонимов.*

Статический анализ программ, которые используют указатели, будет практически невозможен без анализа псевдонимов [19]. Статические анализаторы стали пригодны на практике только с появлением методов по контролю над псевдонимами: внешнепроцедурный анализ Дойча [18] и весьма эффективный чувствительный к потокам анализ Стрингсгарда [28]. Наличие точного и быстрого анализа псевдонимов является обязательным элементом статических анализаторов. В большинстве инструментов производится поверхностный анализ, в том числе с использованием нескольких эвристик, и часто пропускаются псевдонимы [19]. Надо отметить, что в статических анализаторах это делается для того, чтобы уменьшить число ложных срабатываний. В результате появления процессоров с технологией HyperThreading анализаторы, использующие поверхностный анализ, стали демонстрировать совсем плохие результаты. Без учета псевдонимов могут быть пропущены заведомо присутствующие состояния гонки – операции с тем же участком памяти, но названным по-другому или переданным по адресу.

### *4. Вычисления при помощи набора состояний.*

На самом деле, статический анализ построен на исполнении программы, но под исполнением здесь понимают немного другое: выполнение программы на некоторой абстрактной машине, с набором абстрактных нестандартных состояний, подменяющих обычные. Основное понятие – состояние, что есть

набор переменных программы с ассоциированными с ними значениями. В случае с внутри-процедурным анализом в состояние входят локальные переменные, а внешнепроцурный анализ вносит в состояние еще и глобальные переменные, стек. Целью статических анализаторов является связь множества всевозможных состояний со всевозможными моментами исполнения программы. Обычно число таких состояний бесконечно или, по крайней мере, очень велико, поэтому статические анализаторы должны сводить состояния к упрощенному описанию, показывая отношения только между основными переменными, но в статических анализаторах это сводится всего лишь к отслеживанию только возможных значений.

### *5. Анализ участков кода.*

Некоторые методы статического анализа (проверки на основе моделей или формальное математическое доказательство корректности) трудно применить в больших программах. Тогда статический анализ может быть применен к части программы, однако, такой метод не гарантирует корректного результата. Несмотря на то, что статический анализ может быть применен к части программы (кциальному файлу и/или процедуре), такой подход дает плохие результаты – много ложных срабатываний [19]. Но есть и положительные моменты: действительно, часто можно не проверять полностью код на недостающие функции и процедуры.

Статические анализаторы разделяются в свою очередь по типу анализа. Всего разделяют 3 типа анализа:

#### *1. Чувствительные к путям.*

Средства, использующие анализ, чувствительный к путям, анализируют только действующие ветви исполнения программ. Они учитывают переменные и условные конструкции, исключая из обработки недосягаемые ветви исполнения.

#### *2. Нечувствительные к путям.*

Средства анализа, не чувствительные к путям, не производят отсев и рассматривают все варианты исполнения. Этот подход дает более точные результаты, но работает дольше по времени.

### 3. Чувствительные к контексту.

#### a) внешнепроцедурный анализ.

Средства, отслеживающие значения глобальных переменных и параметры функций. В общем случае внешнепроцедурный анализ работает довольно быстро, однако не очень точен. На данный момент не известно чувствительного к контексту средства, позволяющего находить все дефекты кода без ложных срабатываний.

#### б) внутрипроцедурный анализ.

Средства, анализирующие каждую функцию отдельно, вне контекста. Целью большинства разработок статических анализаторов является создание средства с минимальным количеством ложных срабатываний, но на практике анализаторы часто выдают результат, что дефект «возможен».

Одним из первых анализаторов был Lint. Он появился в составе операционной системы Unix 7 и использовался в качестве основного средства контроля качества кода. Со временем средства Lint появилось множество других средств проверки корректности исходного кода. Важно рассмотреть обзор наиболее известных средств статического анализа [13]:

#### 1. Slint.

Slint – средство статической проверки программ на языке С. Представляет собой более современный вариант анализатора lint. Особенность этого средства состоит в том, что оно дает возможность добавить в код специальные аннотации, позволяющие «усилить» проверки качества кода.

#### 2. Cppcheck.

Статический анализатор для проверки кода на языках С и С++. Использует множество проверок, которые не делаются компилятором. В своей основе

использует набор эвристик. Может служить в качестве дополнения к проверкам компилятора и компоновщика. Обнаруживает ограниченное число ошибок и обладает небольшой точностью.

### 3. Clang.

Clang – компилятор, позволяющий осуществлять доступ сторонним приложениям к результатам компиляции. Работает с языками C, C++, Objective-C, Objective-C++. Помимо компилятора содержит встроенный синтаксический анализатор. Аналогично средству `cppcheck` может служить дополнительным средством проверки написанного кода вслед за компилятором и компоновщиком.

### 4. CHESS.

Chess – средство анализа, использующее вместе проверку на основе моделей и динамический анализ. Выявляет ошибки распараллеливания путем систематического анализа планирования и чередования потоков. Способно обнаруживать такие проблемы, как состояние гонки, взаимоблокировки, зависания, активные блокировками и т.д. Проблемы в исходном коде после обнаружения легко исправить, так как этот анализатор дает полностью воспроизводимые результаты. Как и в случае любой другой проверки на основе моделей, систематические исследования обеспечивают полный охват кода тестами – для этого требуется формализовать искомые проблемы в терминах модели, по которой происходит верификация. Помимо проверки на основе моделей, анализатор CHESS работает и в динамическом режиме, т.е. выполняет тест циклически с помощью особого встроенного планировщика. В каждый проход теста выбирается новый вариант распределения процессорного времени между потоками. С другой стороны, это средство проверки на основе моделей, и оно управляет специализированным планировщиком, способным создавать специальное чередование потоков. Для уменьшения вариантов анализа в CHESS применяется частичная редукция и ограничение числа новых контекстов

итераций. Используя ограничение числа контекстов итераций, CHESS не уменьшает глубину расширения пространства состояний, а уменьшает количество переключений потоков в данном сеансе работы приложения.

## 5. PVS-Studio.

PVS-Studio представляет собой коммерческий продукт для выявления ошибок в статическом режиме в программах на языках C, C++ и C++0x. Это средство анализа разработано на основе библиотеки VivaCore с открытым исходным кодом. Данное средство анализа ошибок состоит из нескольких утилит, среди которых VivaMP отвечает за проверку ошибок при многопоточном исполнении кода. Само средство достаточно тяжеловесно и использует много вычислительных ресурсов.

## 6. KISS.

KISS – еще один инструмент для проверки исходного кода, исполняемого в нескольких потоках, на основе моделей. Программы должны быть написаны на языке С. Принцип работы анализатора KISS заключается в том, что он преобразует параллельное приложение на С в последовательное, при этом выбирая способ чередования. После этого выполняется собственно анализ с применением последовательного средства проверки на основе моделей. Далее анализом занимается другая утилита – SLAM.

## 7. SLAM.

SLAM – средство анализа анализирует последовательные программы на основе моделей. Ошибки, выявленные SLAM в последовательной программе, транслируются в ошибки для исходной программы [33]. В худшем случае сложность SLAM оценивается как  $O(P \cdot (G \cdot L)^3)$ , где P – размер программы, G – число глобальных состояний в конечном автомате, L – максимальное число локальных состояний функций. KISS не дает ложных срабатываний.

Статические анализаторы применяются для верификации определенных свойств в программах и проверки соответствия определённым критериям, основываясь только на исходном коде программы. На практике статические анализаторы дают неточный ответ о наличии того или иного свойства в программе, что является проблемой подобных средств анализа программ. В контексте обнаружения состояний гонок в программе статические анализаторы возвращают ответы следующего формата:

- a) если состояние гонки есть, то ответ: гонка должна произойти.

- b) если состояния гонки нет, то ответ: гонки не должно быть.

Основной принцип статического анализа: либо точность, либо время [19]. Отсюда возникает тенденция ложных срабатываний статического анализатора при попытке ускорить анализ, что может привести к бесполезности результата анализа. Таким образом, есть два типа ложного ответа статического анализатора:

- a) false positive: гонки нет, а ответ – гонка должна быть.

- b) false negative: гонка есть, а ответ – гонки не должно быть.

Выбор оптимального сочетания времени работы анализатора и точности является практической задачей, которая разрешается в каждом случае отдельно.

#### **1.4. Метод статического анализа на основе графа совместного исполнения потоков**

При моделировании параллельной программы используется предпосылка – чередование (мультипрограммность) [15], что позволяет упростить анализ реального параллельного вычисления, выполняемого микропроцессорами, и при этом в полной мере представить контекст программы. Чередование позволяет представить выполнение параллельной программы как последовательность дискретных шагов. Для того, чтобы в таком представлении были учтены всевозможные сценарии исполнения программы, и при этом требования к

полноте представления контекста программы не нарушались, необходимо, чтобы инструкции были максимально атомарные [15].

В работе [13-15] была предложена математическая модель обнаружения состояния гонки в многопоточных алгоритмах посредством построения модели взаимного исполнения атомарных инструкций двумя потоками на разделяемой памяти. Общая идея метода сводится к следующим действиям:

1. Для каждого потока выделяются операции, связанные с разделяемыми переменными.

2. Строится граф совместного исполнения потоков на основании операций с разделяемыми переменными в каждом из потоков.

3. Находятся классы эквивалентности полных путей на графе совместного исполнения потоков.

4. Анализируются полные пути на графике совместного исполнения потоков, которые принадлежат разным классам эквивалентности. На основе анализа выбираются пути, для которых возможно состояние гонки.

5. Выделенные пути анализируются, например, с помощью метода неопределенных коэффициентов.

6. По состоянию в финальной вершине делается вывод о наличии гонок.

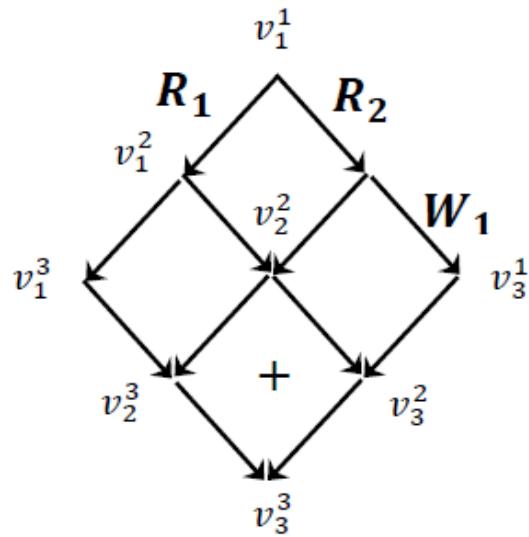

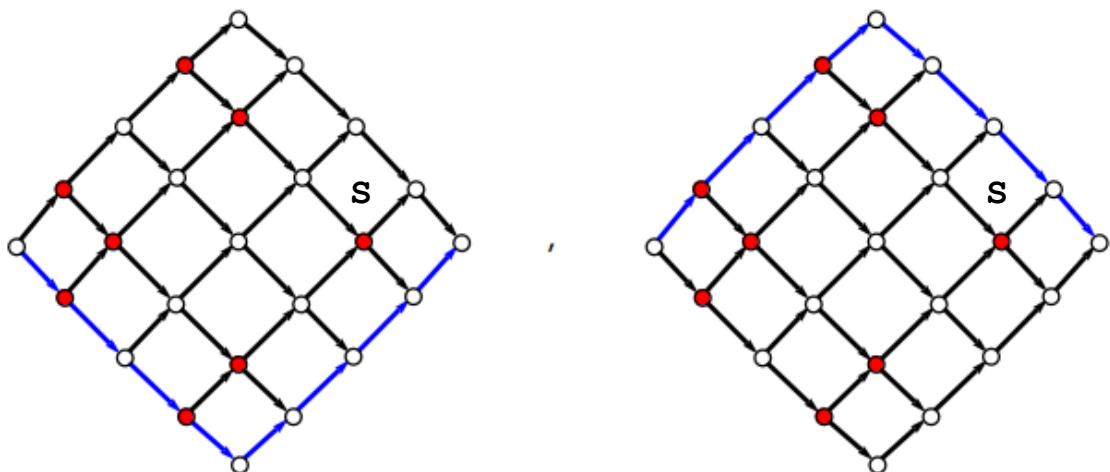

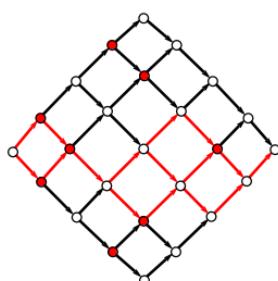

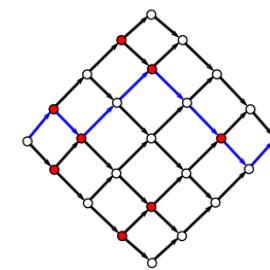

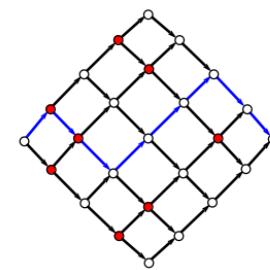

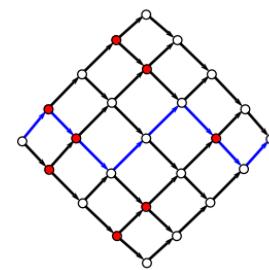

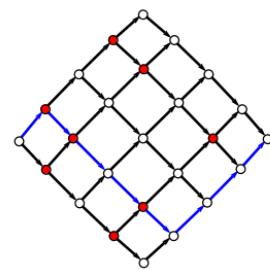

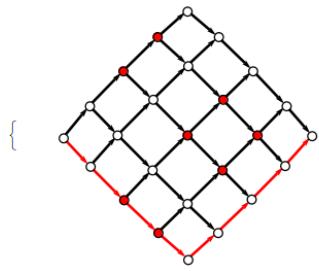

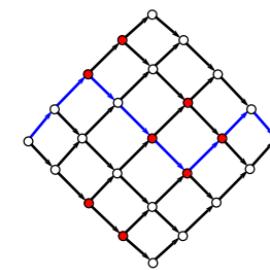

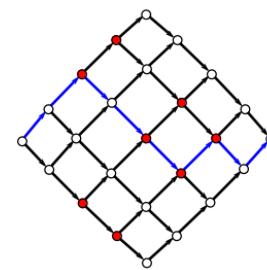

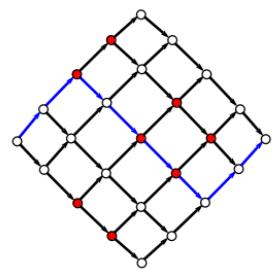

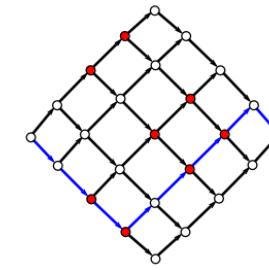

*Граф совместного исполнения потоков* – ориентированный граф, представляющий всевозможные варианты совместного исполнения потоков в многопоточном алгоритме, где каждая дуга ассоциирована с атомарной операцией одного из потока, а вершины – с множеством состояний общей памяти после выполнения очередной атомарной операции. В случае двух потоков исполнения график можно описать следующим образом:

$$G := (V, A): V = \bigcup_{\substack{i=1, k+1 \\ j=1, n+1}} v_j^i, \quad A = \bigcup_{\substack{i=1, k \\ j=1, n+1}} (v_j^i, v_j^{i+1}) \cup \bigcup_{\substack{i=1, k+1 \\ j=1, n}} (v_j^i, v_{j+1}^i), \quad (1)$$

где  $k, n$  – количество операций первого и второго потока соответственно,  $i, j$  – номер атомарной операции первого и второго потока соответственно,  $V$  –

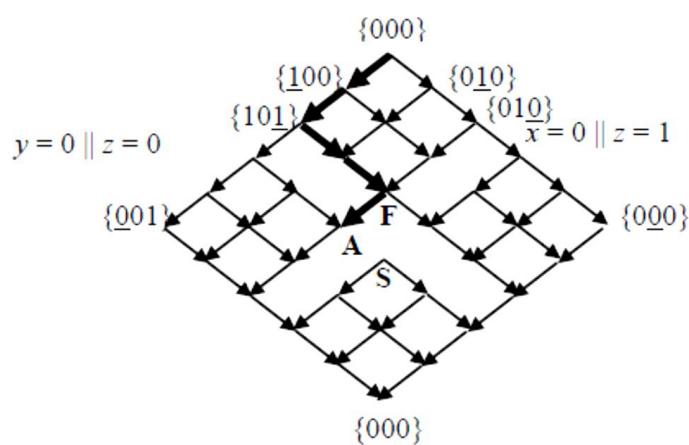

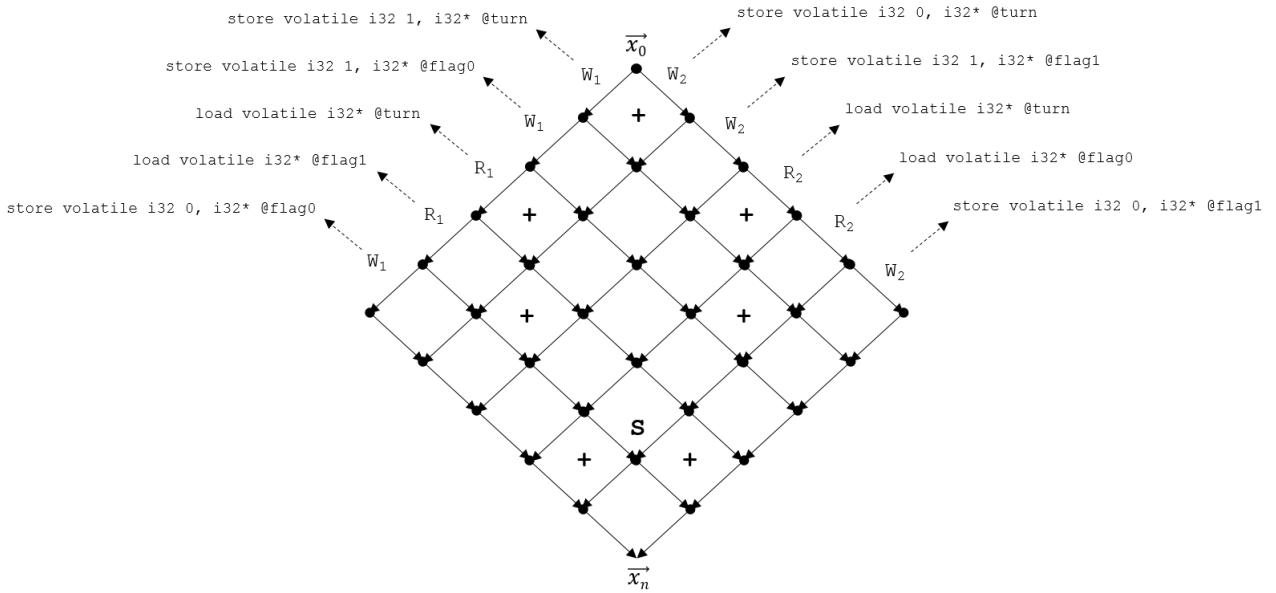

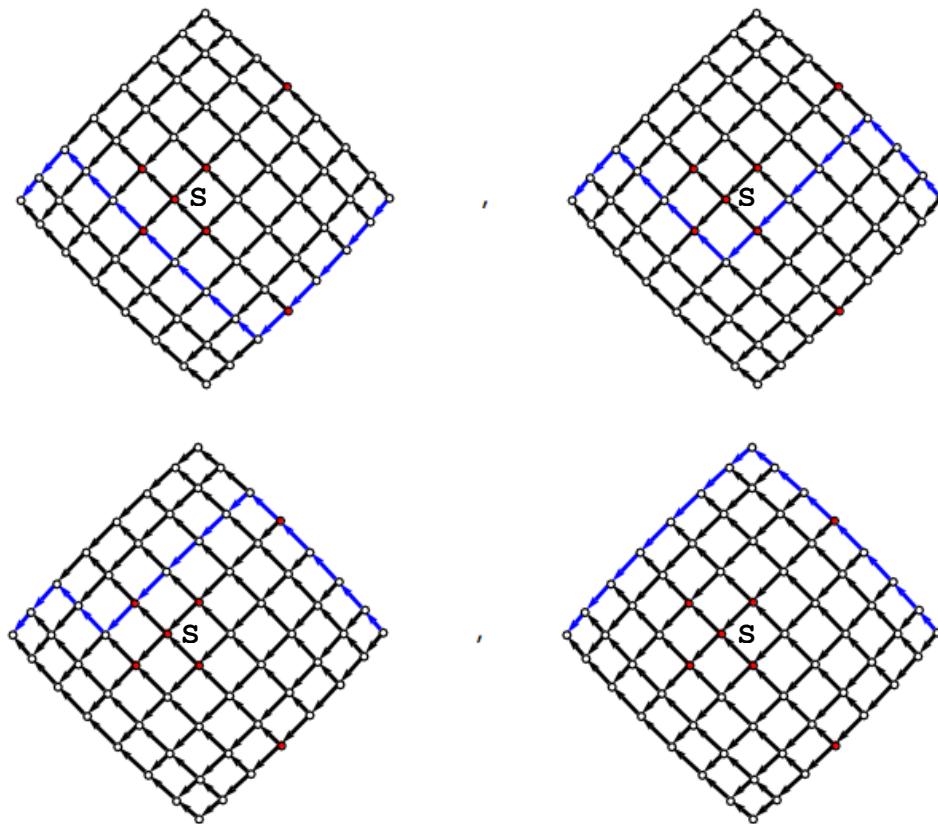

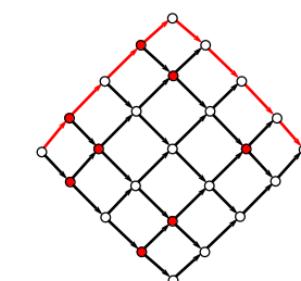

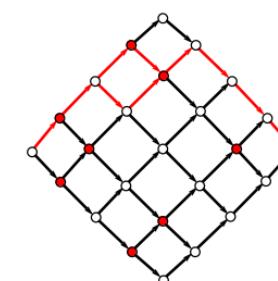

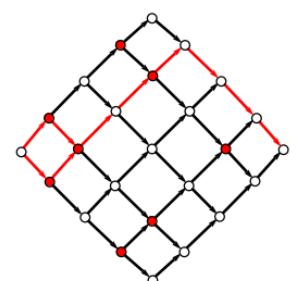

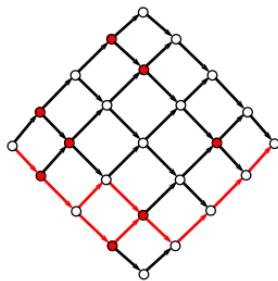

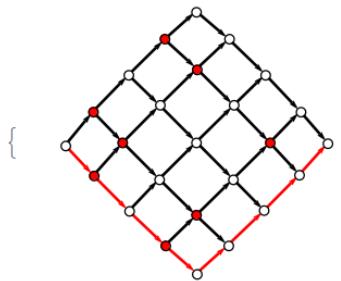

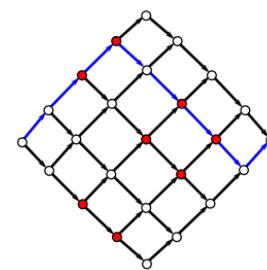

множество вершин графа,  $A$  – множество дуг графа. Пример подобного графа представлен на рис. 2.

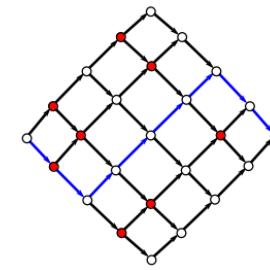

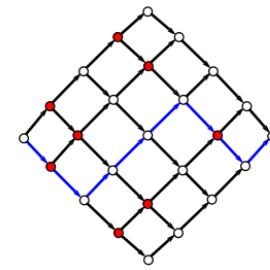

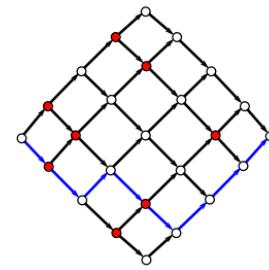

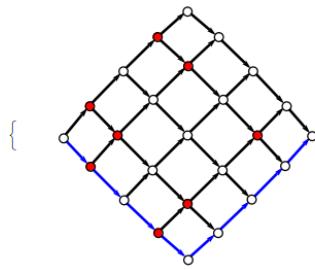

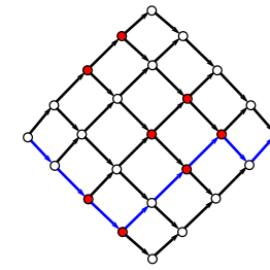

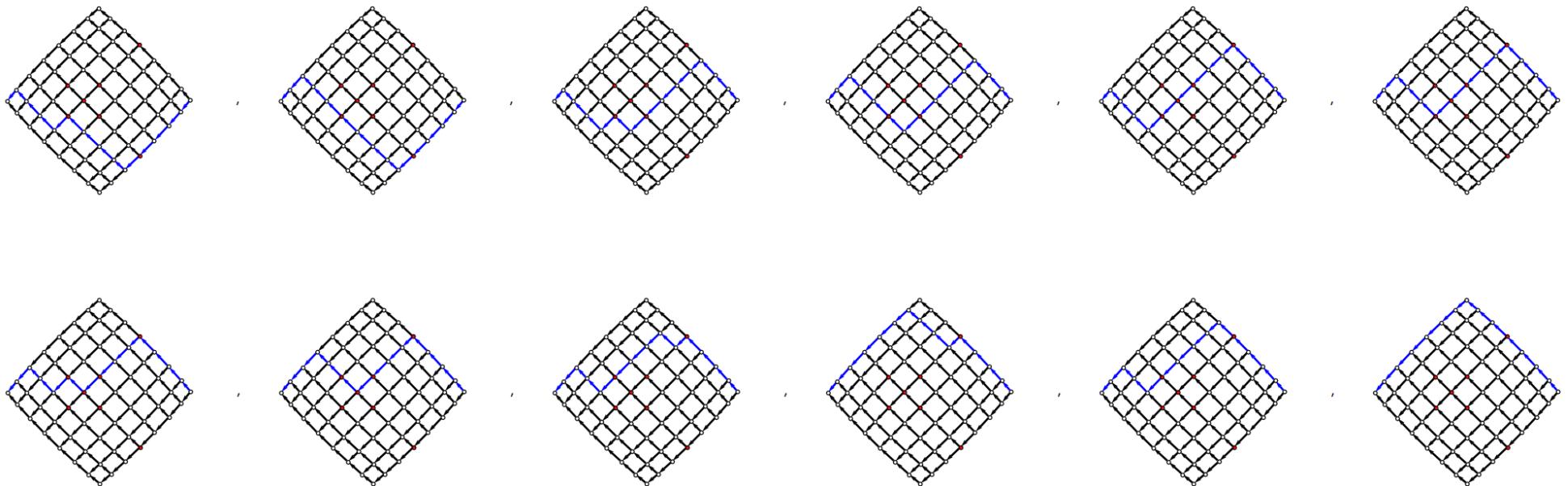

Рис. 2. Граф совместного выполнения двух потоков на разделяемой памяти.

Путям графа  $G$  соответствуют всевозможные варианты исполнения многопоточного алгоритма. Вершинам графа  $V$  соответствует множество состояний общей памяти после выполнения очередной инструкции, дугам  $A$  – атомарные операции над разделяемыми переменными. Каждому ребру поставлена в соответствие операция ( $R$  – чтение,  $W$  – запись) и ячейка памяти, над которой производится операция.

Граф  $G$  имеет вид ромба, в котором начальная вершина находится сверху, а конечная – снизу, а все ребра имеют направление сверху вниз. Начальная вершина определяет вектор исходного состояния взаимодействующих потоков. Начальной вершине сопоставлены значения всех разделяемых переменных после инициализации. Каждое ребро в таком графе определяет единичную атомарную операцию. После совершения потоком очередной операции происходит переход системы из одного состояния в другое по одному из ребер. Конечная вершина характеризует финальное (результатирующее) состояние исполнения потоков.

*Класс эквивалентности* – набор полных путей на графе G, для которых состояние ячейки памяти в конечном узле одинаково.

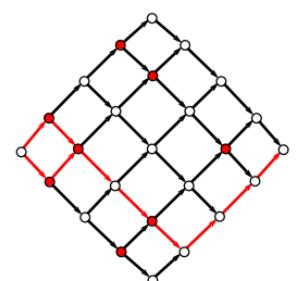

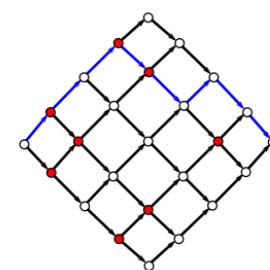

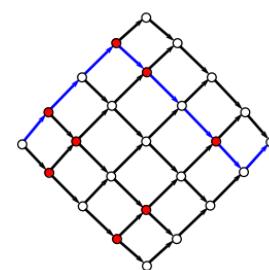

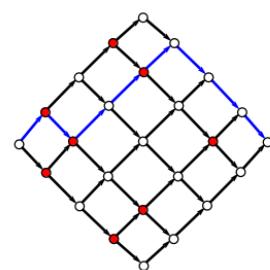

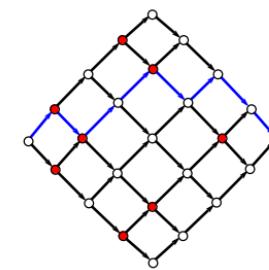

Для нахождения классов эквивалентности необходимо владеть понятием *некоммутирующих операций*. Если существует хотя бы одна общая ячейка памяти, такая что состояние исполнения потоков относительно её после выполнения двух операций может зависеть от их порядка, то будем называть эти операции некоммутирующими, в противном случае скажем, что они коммутируют между собой [14]. Алгоритм поиска классов эквивалентности базируется на понятии некоммутирующих операций. Пример некоммутирующих операций изображен на рис. 3 и обозначен знаком «+».

Рис. 3. Пример указания некоммутирующих операций на графике.

В работе [14] доказывается, что число классов эквивалентности полных путей может быть вычислено за  $O(k \cdot n)$ , где k и n – количество атомарных операций каждого из потоков. Данный факт является сильной стороной метода, указывающий на потенциальную высокую производительность анализа при реализации.

В работе [13] была улучшена математическая модель исследуемого анализа, что позволило расширить применимость метода. Улучшение было достигнуто за счет добавления нового абстрактного представления – расчетного графа,

который строится на основе графа совместного исполнения потоков. С помощью расчетного графа стало возможным учитывать значения всех разделяемых переменных, а не просто общую память.

*Расчетный граф* – конструктивная дискретная модель исходного кода программы, представляющая собой направленный граф, в котором каждому ребру соответствует атомарная операция, а вершинам ставится в соответствие множество значений всех разделяемых переменных.

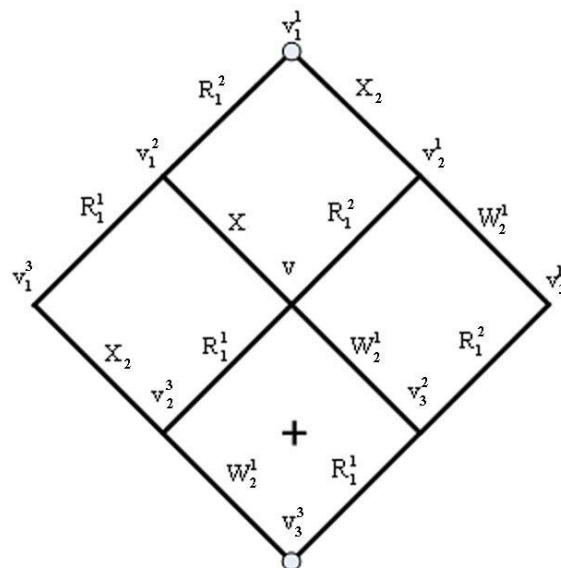

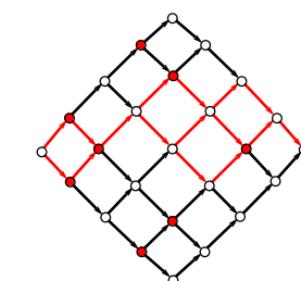

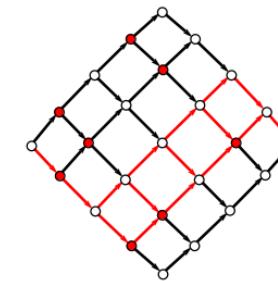

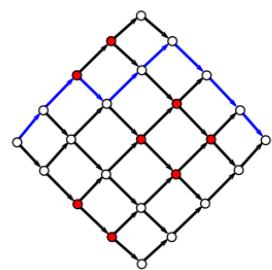

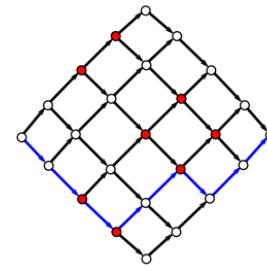

Помимо добавления расчетного графа и анализа значений разделяемых переменных в работе [13] уделено внимание ветвлениюм потока управления и циклам. Предложенное расширение позволяет дополнительно параметризировать некоторые ветвления и анализировать несложные циклы. На рис. 4 показан пример построения расчетного графа на примере алгоритма Петерсона для двух потоков [13].

#### Поток 1:

```

A1: y = 1

A2: z = 0

A3: while(x==1&&z==0);

A4: // critical section

A5: y = 0

```

#### Поток 2:

```

B1: x = 1

B2: z = 1

B3: while(y==1&&z==1);

B4: // critical section

B5: x = 0

```

Рис. 4. Расчетный граф для алгоритма Петерсона.

Модель с расчетным графом является логичным продолжением развития математической модели анализа многопоточных алгоритмов, описанной в работе [14]. Поэтому модель с расчетным графом берется за основу в данной диссертационной работе с целью ее адаптации и реализации для промышленного использования.

В рамках данной работы принимается попытка адаптации математической модели при анализе контекста программы, полученного вследствие линеаризации графа потока управления. Поэтому интересно также привести описание гонки в терминах математической модели исследуемого метода статического анализа.

Гонка (в терминах графа  $G$ , описанный в (1)) – существование двух разных полных путей, для которых в финальном состоянии состояния хотя бы одной из ячеек памяти различны. С учётом начальных значений ячеек и того, как их значения меняются, используем метод неопределенных коэффициентов. На каждом ветвлении добавляем коэффициент  $\alpha \in \{0, 1\}$  к изменению в левой ветви и  $(1-\alpha)$  – правой. Множество неопределенных коэффициентов  $D$  полностью описывает путь на графике. В финальной вершине имеем множество значений, где каждая ячейка памяти в общем случае имеет вид [13]:

$$x_i = f_i(\vec{x}_0, D), \quad (2)$$

где  $\vec{x}_0$  – состояние всех ячеек памяти в начальной вершине,  $D$  – значения неопределенных коэффициентов,  $f_i$  – некоторая функция, определенная для каждой из ячеек. Исходя из определения понятия гонки и принципов построения и анализа графа, изложенных выше, получаем, что гонка возможна тогда и только тогда, когда [13]:

$$\exists i, D_1, D_2: f_i(\vec{x}_0, D_1) \neq f_i(\vec{x}_0, D_2), \quad (3)$$

где  $D_1$  и  $D_2$  – множества бинарных коэффициентов.

## Глава 2. Реализации модели статического анализа нахождения состояния гонки в многопоточных алгоритмах с использованием линеаризованного графа потока управления

### 2.1. Анализ оптимизаций на промежуточном представлении

В работе был взят за основу компилятор CLANG&LLVM как наиболее активно развивающийся и обладающий рядом преимуществ с точки зрения гибкости реализации и удобства адаптирования под конкретные случаи и задачи. CLANG&LLVM для проведения оптимизаций использует платформонезависимый IR в SSA (Static Single Assignment) форме, причем CLANG выступает front-end'ом, транслируя язык высокого уровня в IR нужного вида (LLVM IR), а LLVM – оптимизирующим компилятором, который проводит необходимые оптимизации, трансформации или программный анализ на LLVM IR и затем транслирует финальный LLVM IR в бинарный код целевой архитектуры. Общая структура использования компилятора представлена на рис. 5.

Рис. 5. Структура компиляции с помощью CLANG&LLVM.

Форма статического единственного присваивания (SSA) является одной из самых распространенных форм представления потока данных программы и

активно используется в большинстве современных оптимизирующих компиляторов [26]. В SSA-форме любая переменная может быть определена только один раз, вследствие чего для соблюдения данного ограничения должны выполняться следующие условия:

- Наличие  $\phi$ -узлов в точках схождения потока управления.  $\phi$ -узел для *переменной* – это операция, выбирающая среди множества значений переменной нужное.

- Переименование всех переменных так, чтобы каждому определению соответствовала своя уникальная переменная.

LLVM содержит более 100 уникальных оптимизаций, которые были проанализированы с точки зрения влияния на CFG. Предлагается рассмотреть и оценить влияние следующих оптимизаций, которые часто имеют свою реализацию в оптимизирующих компиляторах:

- If-conversions – перевод в предикатное представление [12].

Современные EPIC-архитектуры поддерживают предикатное вычисление, что позволяет выполнять операции раньше перехода, ведущего на соответствующий участок. Операции, вынесенные выше перехода, исполняются под условием (предикатом) этого перехода. Используя поддержку предикатных вычислений, можно преобразовать ациклический регион программы, состоящий из нескольких линейных участков, в один линейный участок. При этом действии будут удалены все внутренние переходы ациклического региона. По сути, if-conversion преобразует зависимости по управлению с операциями переходов в зависимости по данным с предикатами. В рамках выбранного оптимизирующего компилятора CLANG&LLVM преобразование промежуточного представления в предикатную форму не реализовано, но предоставлен соответствующий API [22], который позволяет оперировать с нужными структурами IR и его представлениями. Таким образом, основываясь на

известных алгоритмах преобразования и общепринятых практиках [11, 26], можем сделать вывод, что возможна реализация if-conversion.

- Трансформация циклов:

В современных оптимизирующих компиляторах реализованы десятки или даже сотни различных трансформаций циклов, некоторые из них можно отнести к оптимизациям, применение которых неявно приводит к линеаризации CFG. Эти и множество других трансформаций циклов подробно описаны в обзорной статье [17]. В рамках данной работы рассмотрены такие оптимизации CLANG&LLVM, применение которых с практической точки зрения наилучшим образом отвечают задаче линеаризации CFG. Согласно официальной документации оптимизирующего компилятора LLVM [24] возможно применить следующие оптимизации к циклам на IR, полученный в данном случае с помощью CLANG:

- *-lcssa (Loop-Closed SSA Form Pass)*

Оптимизация изменяет циклы путем переноса фи-узлов в конец циклов для всех значений, которые остаются живыми за границами цикла.

Например:

```

for (...)           for (...)

if (c)           if (c)

x1 = ...       x1 = ...

else             ->      else

x2 = ...       x2 = ...

x3 = phi(x1, x2) x3 = phi(x1, x2)

... = x3 + 4     x4 = phi(x3)

... = x4 + 4

```

Дополнительные фи-узлы являются излишними, но они легко удалятся после оптимизации InstCombine. Основная выгода данной трансформации – это сделать применение других цикловых оптимизаций, таких как LoopUnswitch, более простыми.

- *-licm (Loop Invariant Code Motion)*

Оптимизация выполняет перемещение инвариантного кода в цикле, пытаясь удалить как можно больше кода из тела цикла.

- *-loop-deletion (Delete dead loops)*

Оптимизация отвечает за удаление циклов, которые не вносят вклад в возвращаемое значение функции.

- *-loop-reduce (Loop Strength Reduction)*

Оптимизация проводит понижение стоимости выражений с индуктивными переменными, заменяя дорогие операции на более дешевые. В частности, выражения с массивами изменяют так, чтобы была возможность воспользоваться преимуществами расширенного режима адресации индекса (scaled-index addressing modes), упрощающее обращение к элементам массивов.

- *-loop-rotate (Rotate Loops)*

Оптимизация выполняет простое вращение цикла.

- *-loop-simplify (Canonicalize natural loops)*

Оптимизация выполняет несколько трансформаций над естественными циклами, преобразуя их в более простую форму, которая позволяет делать последующий анализ и трансформации проще и эффективнее, например, для LICM (Loop Invariant Code Motion). Данная оптимизация создает дополнительный узел (предцикл) перед головой цикла, что гарантирует наличие только единственной входной дуги в цикл. Также гарантируется, что после применения оптимизации измененный цикл будет иметь только одну обратную дугу.

- *-loop-unroll (Unroll loops)*

Оптимизация реализует простую раскрутку цикла, которая заключается в создании несколько копий итераций цикла (число копий n называет фактором развертки) и в увеличении шага цикла в это же число раз.

Например, развертка с фактором 2:

```

for (i = 0; i < n; i++)           for (i = 0; i < n-1; i+=2) {

```

```

a[i] = b[i] + c[i];

a[i] = b[i] + c[i];

->      a[i+1] = b[i+1] + c[i+1];

}

for (; i < n; i++)

a[i] = b[i] + c[i];

```

Оптимизацию стоит применять после исполнения оптимизации *-indvars* (Canonicalize Induction Variables), когда циклы приведены к каноническому виду, что позволяет легко определять число итераций циклов.

- *-loop-unswitch (Unswitch loops)*

Оптимизация изменяет циклы, которые содержат переходы на инвариантные для цикла условные операции для того, чтобы создать несколько циклов. Например:

```

for (...) if (lic)

A for (...)

if (lic) -> A; B; C

B else

C for ...

A; C

```

Ожидается, что оптимизация LICM исполняется раньше, что делает возможность применение данной оптимизации очевиднее.

- *-loop-idiom (Recognize loop idioms)*

Оптимизация реализует распознаватель идиом, который трансформирует простые циклы в бесцикловую форму.

- *-loop-instsimplify (Simplify instructions in loops)*

Оптимизация проводит легкое упрощение инструкций в теле цикла.

Среди представленных оптимизаций LLVM можно выбрать те, которые могут привести к существенному изменению CFG, а также прочих представлений IR, что в конечном итоге повышает линеаризацию CFG программ и упрощает различные виды статического анализа кода программ на предмет

состояния гонок. Стоит заметить, что для успешной линеаризации CFG программ важно не только применить необходимые оптимизации компилятора LLVM, но и правильно подобрать последовательность запусков оптимизаций, так как оптимизации могут быть конфликтующими – применимость одной приводит к неприменимости другой, и наоборот, связанными – неприменимость одной влечёт неприменимость другой [10].

Таким образом, наибольший интерес с точки зрения влияния на CFG вызывают следующие оптимизации:

- *-lcssa,*

- *-loop-simplify,*

- *-licm,*

- *-loop-reduce,*

- *-loop-unroll,*

- *-loop-unswitch.*

## 2.2. Линеаризация графа потока управления через линейку оптимизаций LLVM

Компилятор позволяет создавать свою собственную линейку оптимизаций либо использовать стандартную. Стандартных линеек оптимизаций у LLVM три: O1, O2, O3. Их также называют уровнями оптимизаций, где O1 – минимальный набор оптимизаций, а O3 – максимальный. Согласно документации LLVM интересуемый набор оптимизаций, выявленный в п.2.1, содержится во втором уровне оптимизации LLVM – O2. Таким образом, чтобы получить минимальный эффект от данных оптимизаций во время компиляции для оценки достаточно использовать второй уровень оптимизации O2.

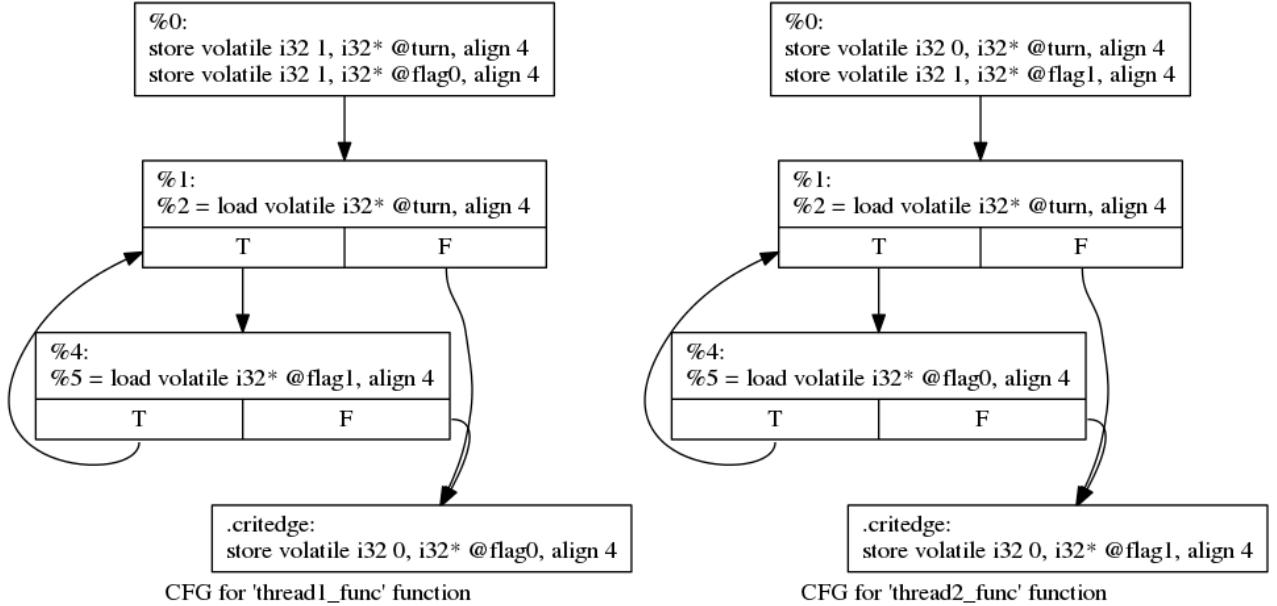

В качестве примера интересно рассмотреть CFG-графы взаимоисключающего алгоритма Петерсона для 2 потоков, одна из реализаций которого на языке Си выглядит следующим образом:

```

/* Algorithm of Peterson */

#include <stdio.h>

#include <stdlib.h>

#include <pthread.h>

int volatile turn = 0;

int volatile flag0 = 0;

int volatile flag1 = 0;

static void *thread1_func ( void * args_ptr )

{

turn = 1;

flag0 = 1;

while ( turn == 1 && flag1 == 1 );

/* Critical section ****/

flag0 = 0;

return NULL;

}

static void *thread2_func ( void * args_ptr )

{

turn = 0;

flag1 = 1;

while ( turn == 0 && flag0 == 1 );

/* Critical section ****/

flag1 = 0;

return NULL;

}

int main () {

pthread_t thread1,thread2;

if (pthread_create(&thread1, NULL, thread1_func, NULL) != 0)

{

return EXIT_FAILURE;

}

if (pthread_create(&thread2, NULL, thread2_func, NULL) != 0)

{

return EXIT_FAILURE;

}

if (pthread_join(thread1, NULL) != 0)

{

return EXIT_FAILURE;

}

if (pthread_join(thread2, NULL) != 0)

{

return EXIT_FAILURE;

}

return 0;

}

```

Важным нюансом в представленной реализации алгоритма Петерсона является использование примитива «volatile». При применении большого количества оптимизаций компилятор, как правило, не знает о разделяемых переменных в коде, что может привести к неправильной генерации кода целевой архитектуры. Например, разделяемые переменные могут и вовсе быть удалены из процедур, исполняемых потоками. Таким образом, разработчику необходимо следить за расстановкой барьеров записи в память в случае активного использования оптимизаций компиляторов.

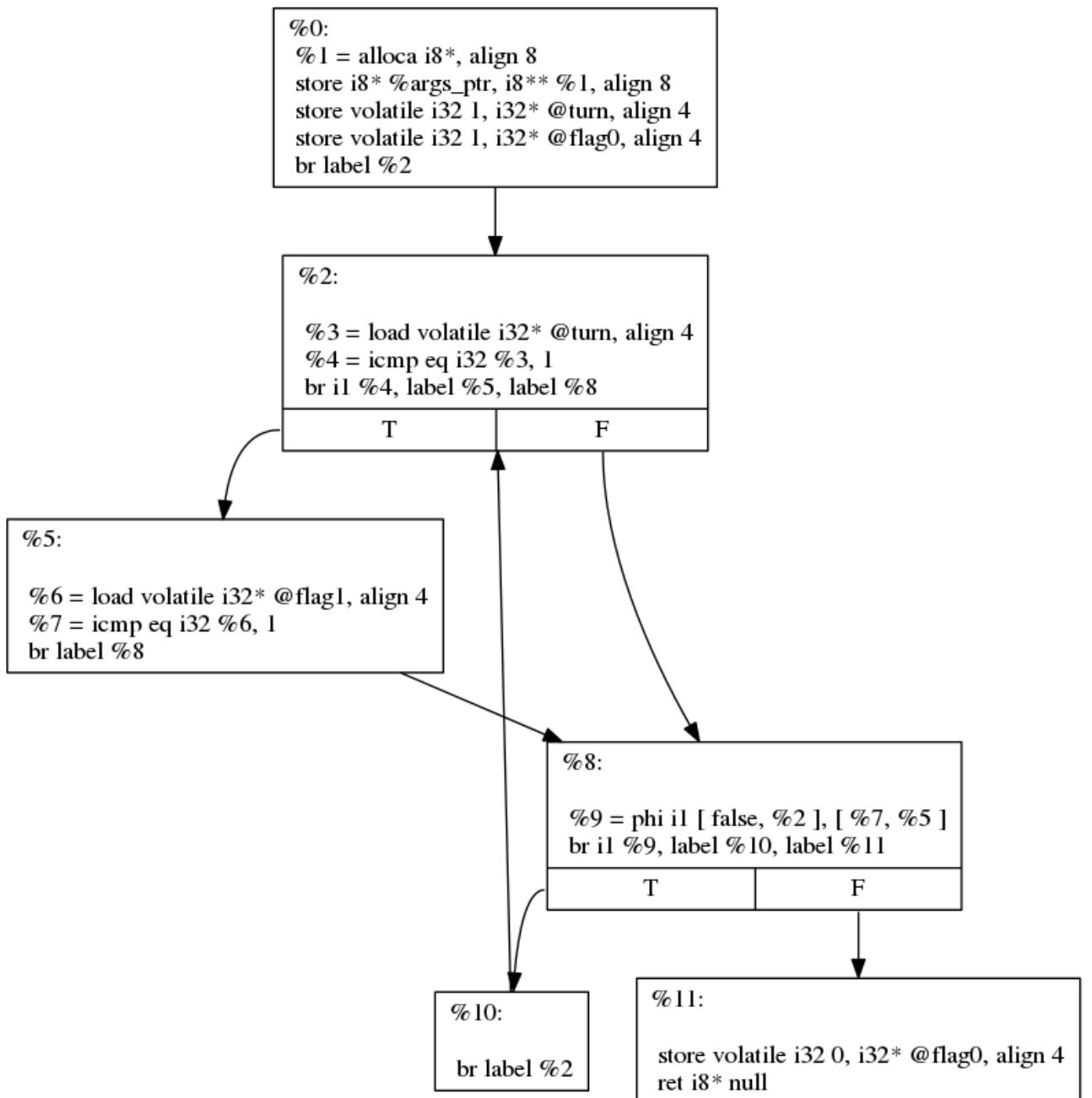

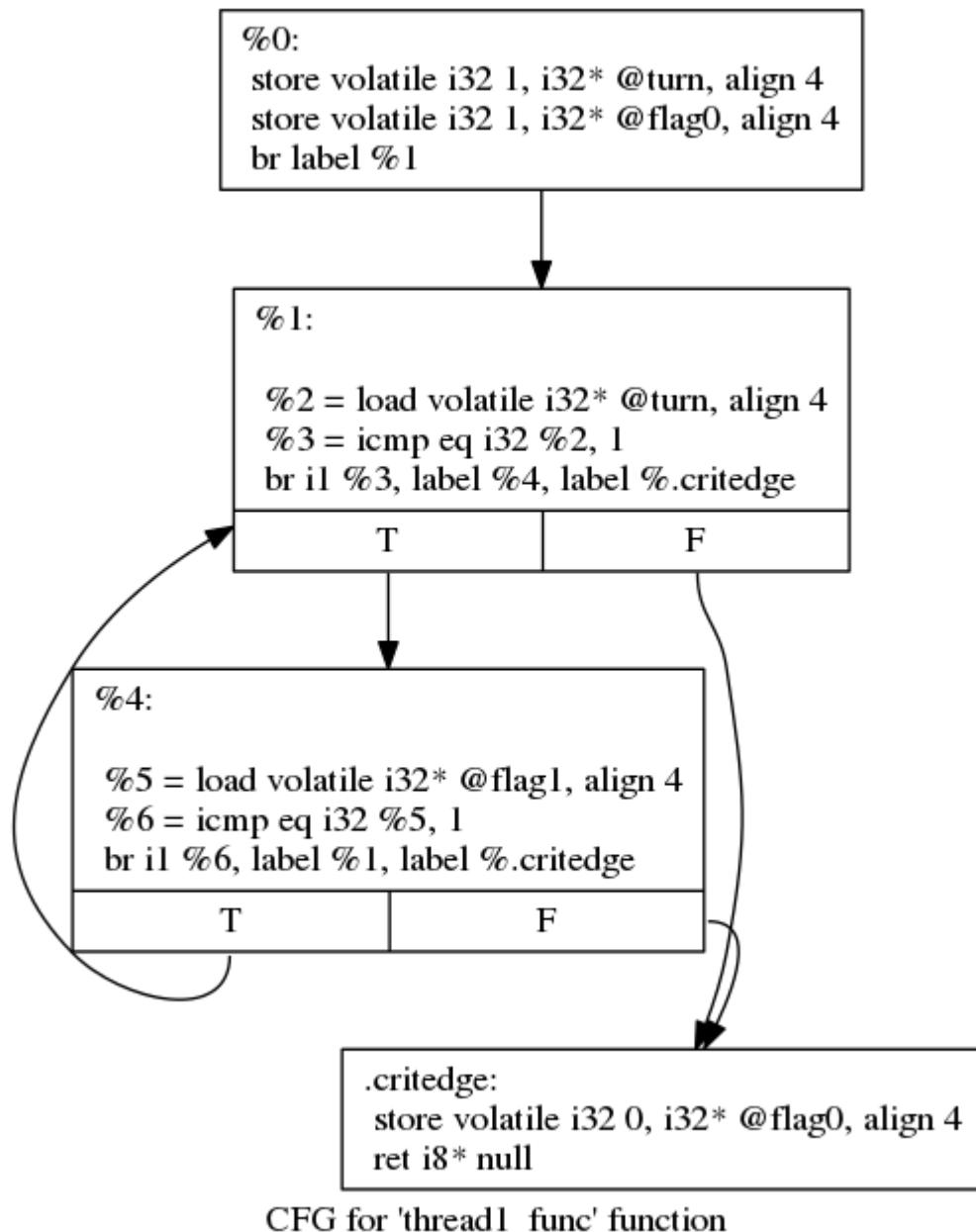

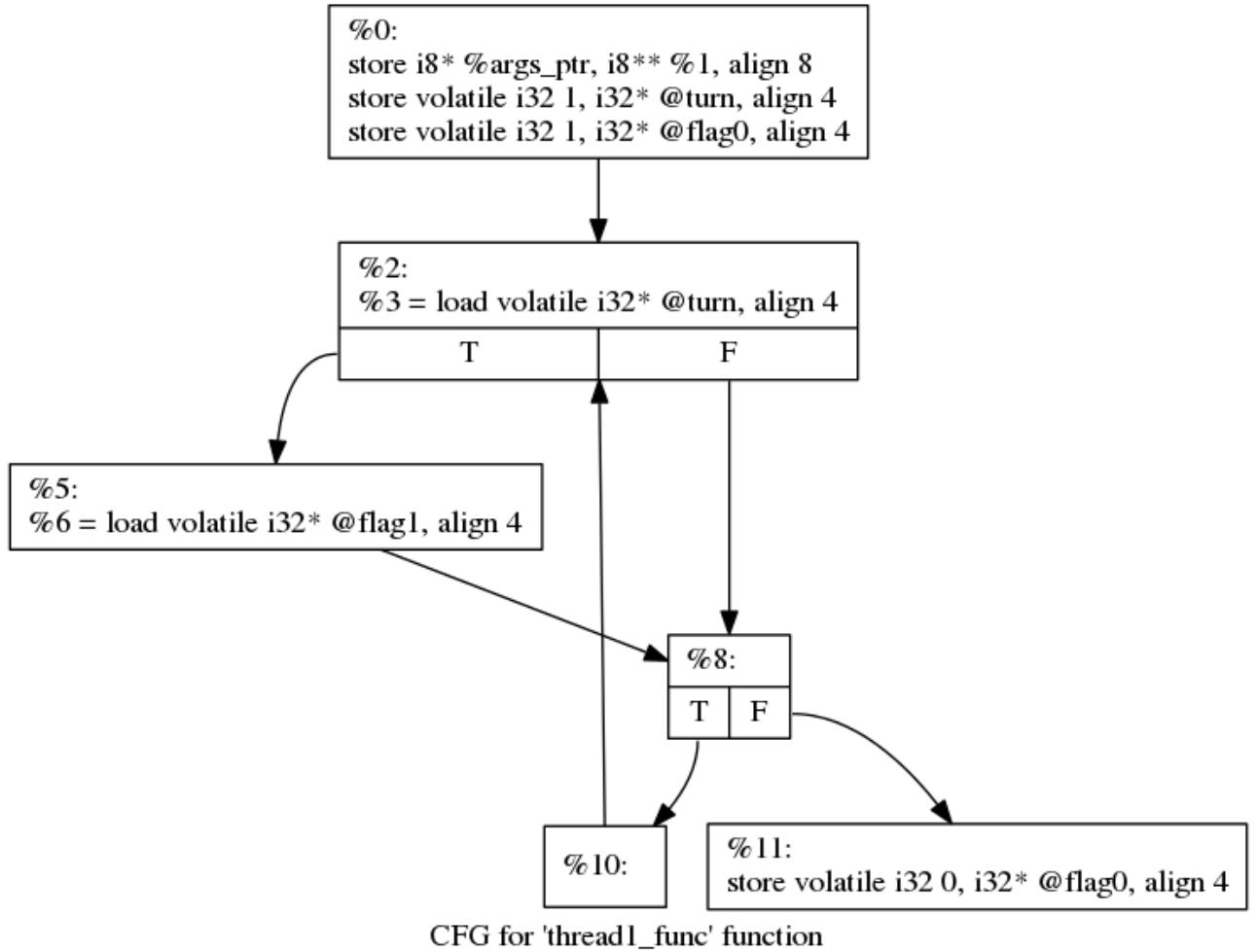

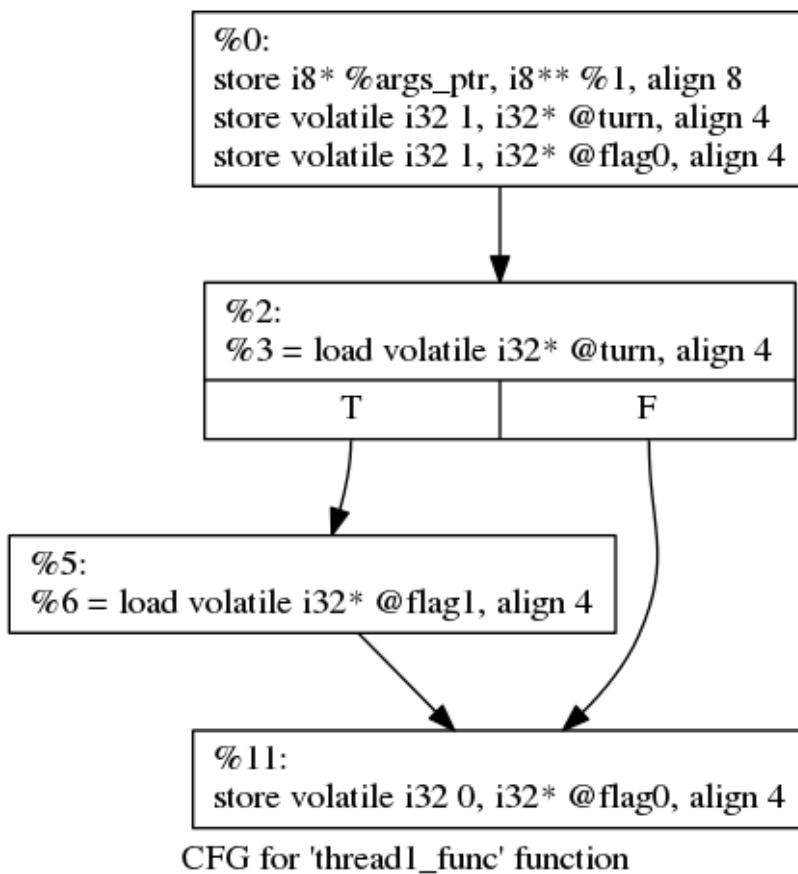

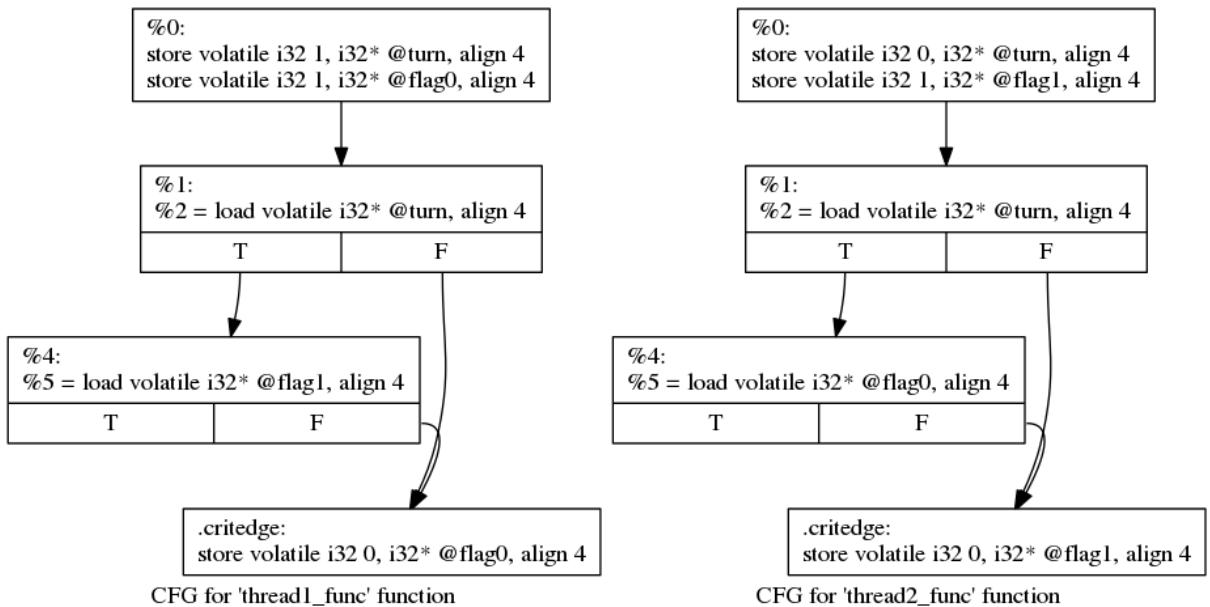

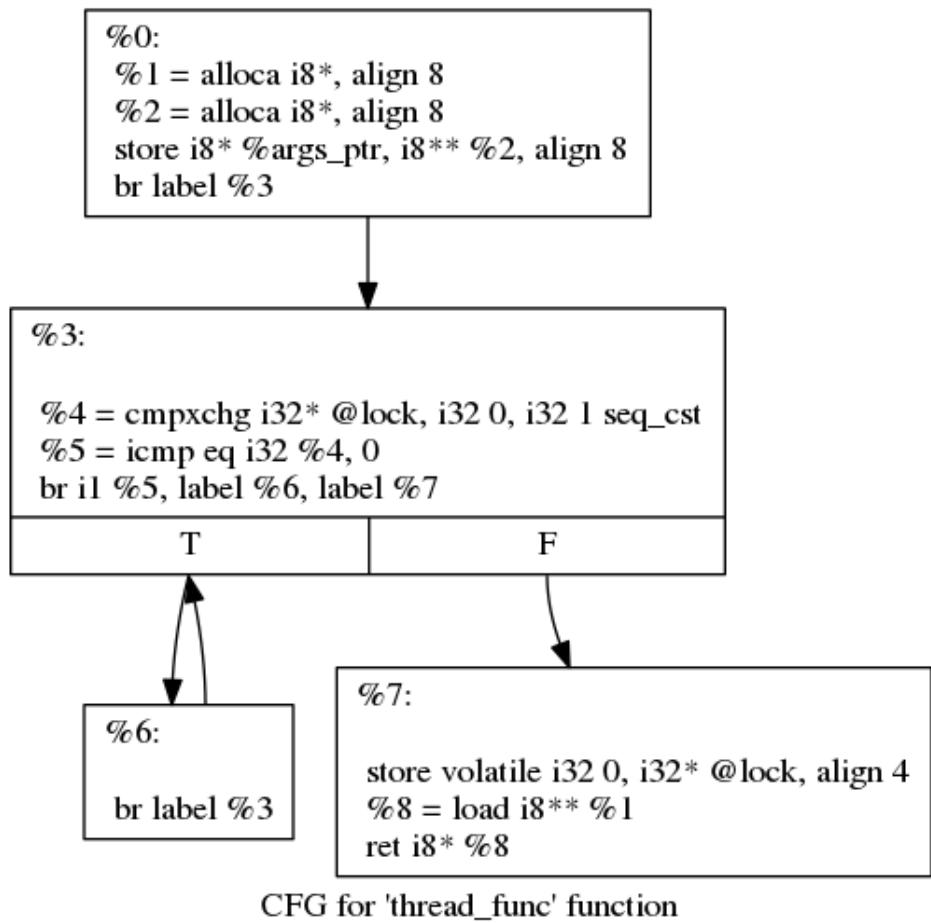

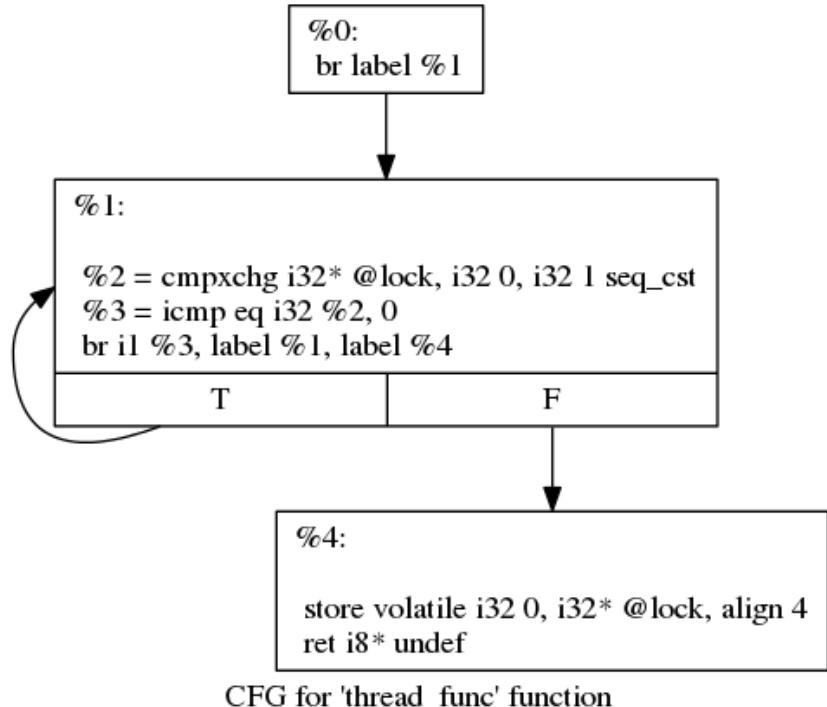

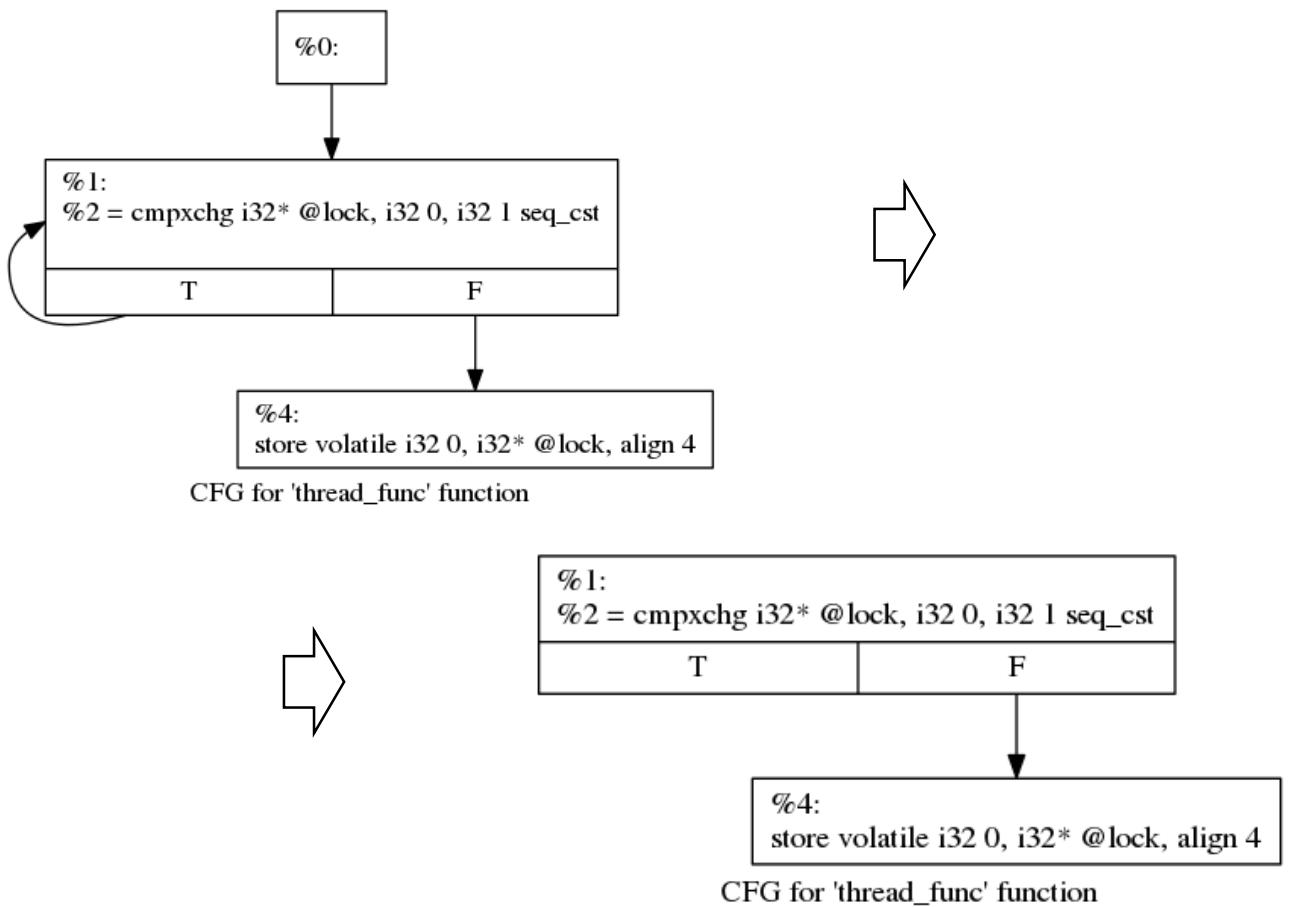

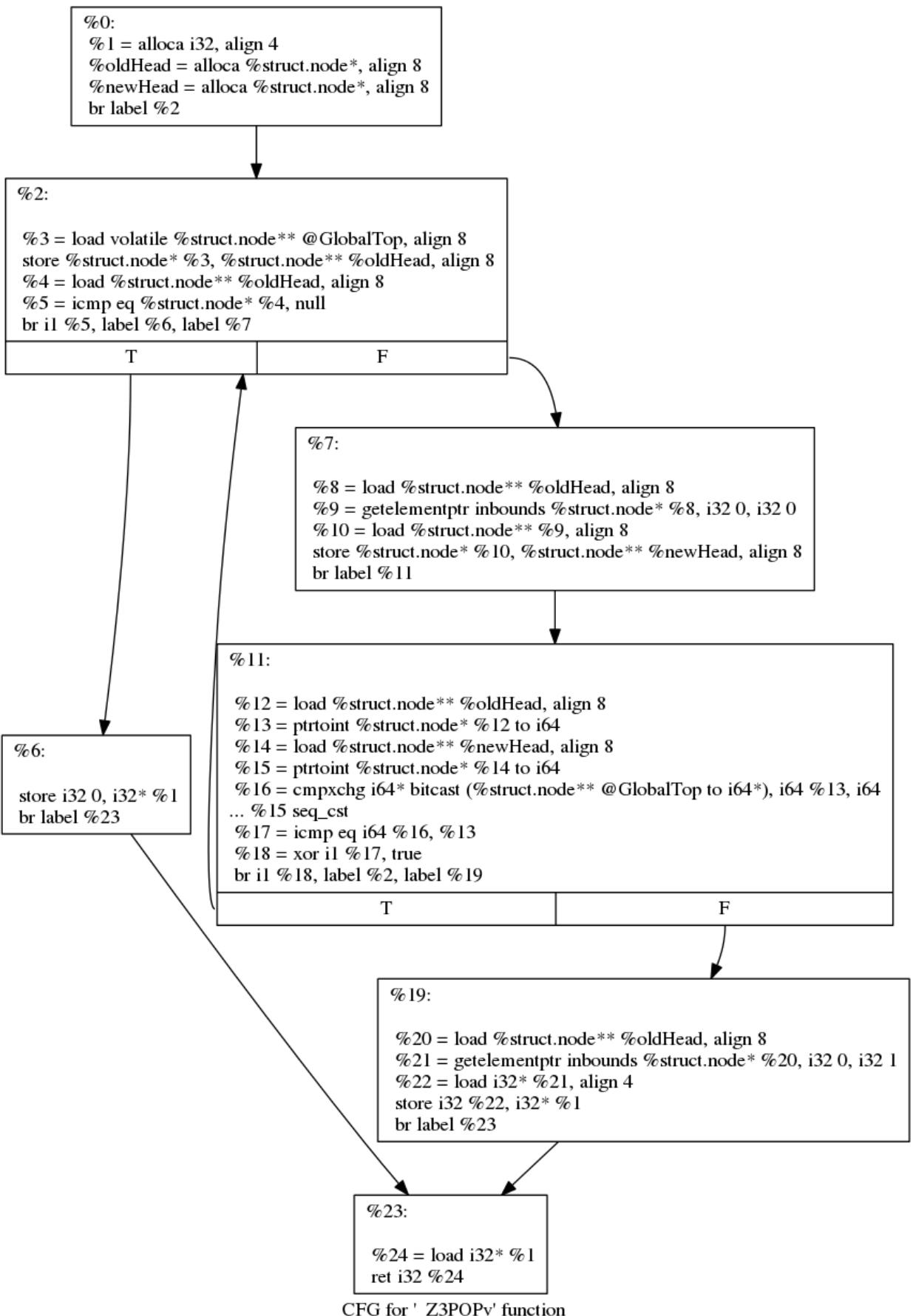

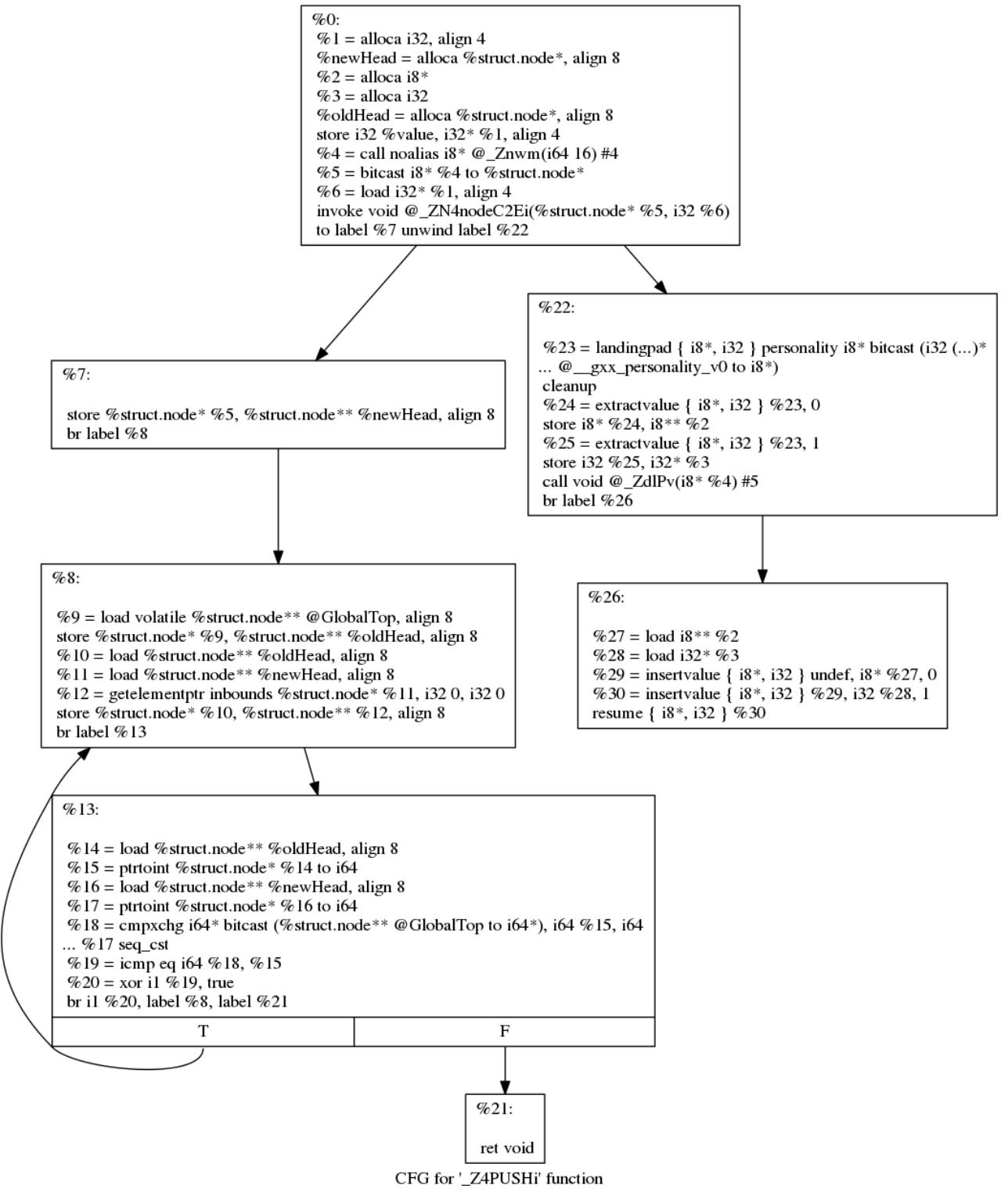

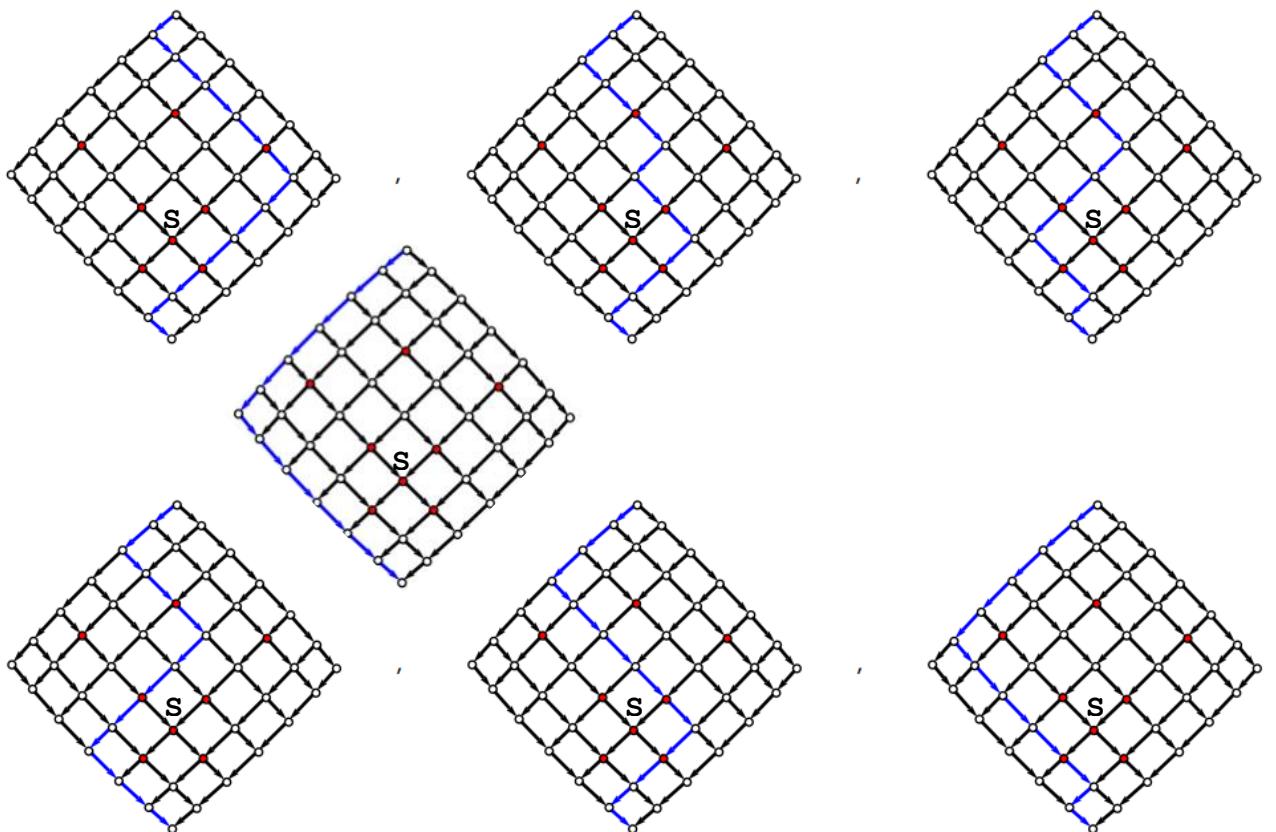

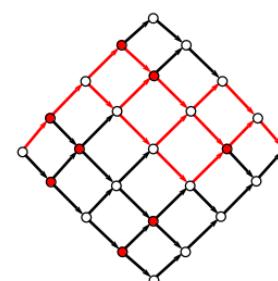

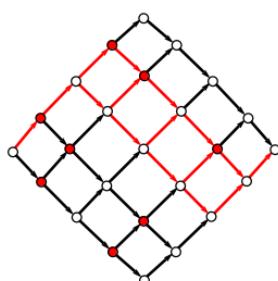

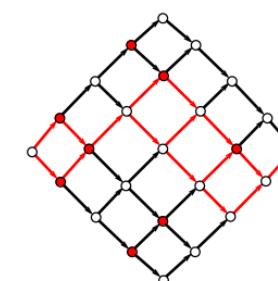

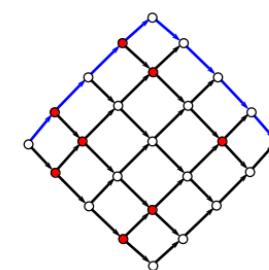

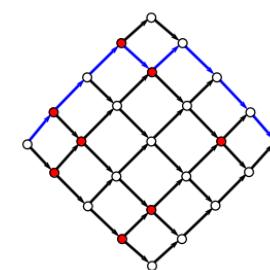

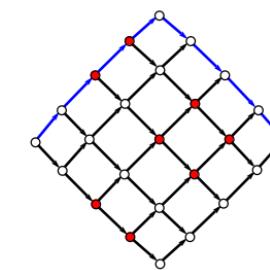

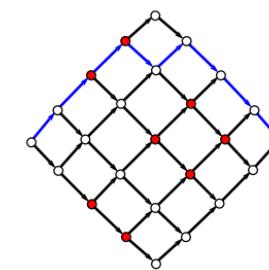

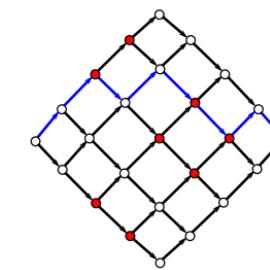

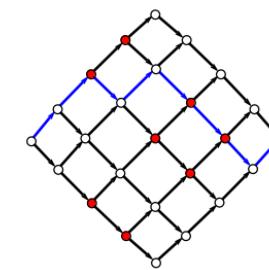

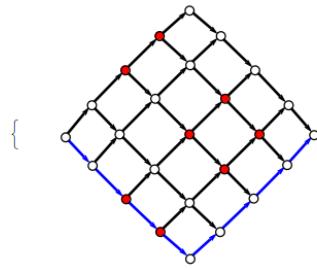

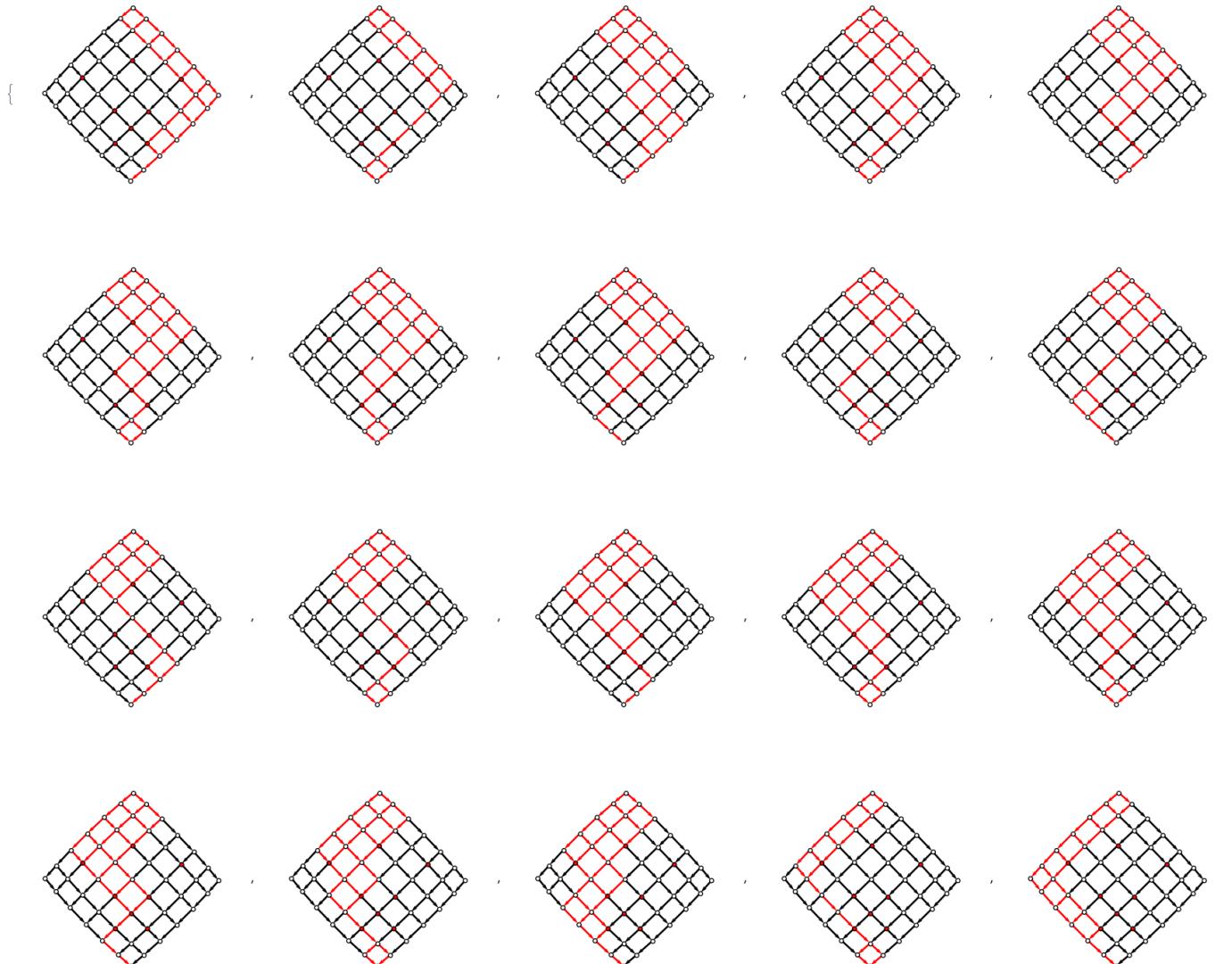

Поскольку программный код обоих treadов симметричен, то рассмотрим CFG одного из них на промежуточном представлении LLVM до оптимизаций и после применения интересуемых нас линейки оптимизаций. На рис. 6 и рис. 7 изображен CFG «thread1\_func» до и после применения оптимизаций соответственно. Функционал LLVM позволяет получать промежуточное представление с различных фаз линейки компилятора в DOT-представлении, которые легко визуализируются различными утилитами для построения графов. Таким образом, в процессе применения метода статического анализа кода на предмет состояния гонок в многопоточном алгоритме дополнительно появляется удобное, быстрое и ясное средство визуализации, что повышает глубину анализа и упрощает применимость метода.

На рис. 6 видно, что на оптимизированном LLVM IR уменьшилось не только количество инструкций, но и ветвлений потока управления. Эффект от применения оптимизаций на реальных задачах будет больше, что сделает применение статического анализа более доступным [5].

Как видно на рис. 6, появились новые аналитические структуры – ф-узлы, которые ранее с точки зрения математической модели не анализировались. Докажем в следующем параграфе, что ф-узел в LLVM IR не влияет на анализ кода и на выводы о наличии состояний гонок в программном коде многопоточного алгоритма.

Рис. 6. CFG треда в алгоритме Петерсона до применения оптимизаций.

Рис. 7. CFG треда в алгоритме Петерсона после применения оптимизаций.

### 2.3. Анализ инструкций SSA-формы LLVM IR, не влияющих на математическую модель поиска RC

Исследуемый метод статического анализа многопоточных алгоритмов основывается на графе совместного исполнения потоков, узлы которого – атомарные операции. Данная особенность метода позволяет иначе взглянуть на

промежуточное представление программы. Можно смело утверждать, что некоторые инструкции IR программы могут быть удалены из анализируемого контекста программы в силу их не влияния на процесс анализа в рамках исследуемого метода. Поставим перед собой задачу выявления тех инструкций IR, которые не влияют на метод статического анализа, а также задачу доказательства не влияния обнаруженных инструкций [1, 4].

На промежуточном представлении атомарными операциями являются инструкции LLVM IR в SSA-форме. В свою очередь из определения о RC следует, что конкурентный доступ к памяти осуществляется через атомарные операции чтения/записи, которые в LLVM IR представляют собой инструкции `load` и `store`. Рассмотрим семантику данных инструкций [23]:

```

<result> = load [volatile] <ty>* <pointer>[, align <alignment>] [, !nontemporal !<index>] [, !invariant.load !<index>]

<result> = load atomic [volatile] <ty>* <pointer> [singlethread] <ordering>, align <alignment>

!<index> = !{ i32 1 }

store [volatile] <ty> <value>, <ty>* <pointer>[, align <alignment>] [, !nontemporal !<index>]

store atomic [volatile] <ty> <value>, <ty>* <pointer> [singlethread] <ordering>, align <alignment>

```

Как видно из семантики инструкций `load` и `store` операция чтения/записи всегда происходит через указатель на память, а результат сохраняется в уникальную переменную согласно SSA-формы. Таким образом, данные инструкции оперируют и с регистрами, и с памятью. Отсюда **можно сделать вывод, что инструкции, оперирующие только с регистрами (виртуальными регистрами или временными переменными в SSA-форме), не представляют интереса в методе статического анализа, т.к. не влияют на возникновения RC.**

Анализируя многопоточные алгоритмы, нельзя не упомянуть класс инструкций, которые атомарно делают несколько операций, в том числе и

операции с памятью. Такие инструкции поддерживаются как на уровне микропроцессоров, так и на уровне ядра операционной системы. Поэтому в зависимости от вида операционной системы и архитектуры микропроцессора многообразие специальных инструкций для работы с памятью может отличаться, но, как правило, наблюдается общая концепция – выполнение нескольких операций за единый неделимый период времени: чтение из памяти, сравнение и изменение состояния памяти в зависимости от результатов сравнения. Ярким примером такой инструкции является CAS (Compare and Swap/Set), которая применяется в реализации неблокирующих алгоритмов. В LLVM IR инструкциями, проводящие атомарно несколько операций над памятью, являются следующие [23]:

1. «CMPXCHG» – читает из памяти значение и сравнивает его с переданным аргументом. Если значения равны, то в память сохраняется новое значение, переданное очередным аргументом.

```

cmpxchg [weak] [volatile] <ty>* <pointer>, <ty> <cmp>, <ty>

<new> [singlethread] <success ordering> <failure ordering> ;

yields { ty, i1 }

```

2. «ATOMICRMW» – осуществляет различные операции над значением в памяти, где первый аргумент – тип операции (сложение, вычитание, сравнение и т.д.), второй аргумент – адрес в памяти, третий аргумент – значение-аргумент к осуществляющей операции.

```

atomicrmw [volatile] <operation> <ty>* <pointer>, <ty> <value>

[singlethread] <ordering> ; yields ty

```

**Таким образом, заключаем, что класс атомарных операций типа CAS нельзя удалять из контекста программы, так как они непосредственно могут создать RC в параллельной программе.**

SSA форма промежуточного представления обуславливает наличие ф-узлов. Докажем, что ф-узел не влияет на исследуемый метод статического анализа [4, 8]. В LLVM IR ф-узел называется ф-инструкцией. Особенность SSA-формы LLVM IR [6] включает в себя то, что все ф-инструкции в узлах графа потока

управления располагаются в начале, и до них не может быть никаких других инструкций. При этом ф-инструкция имеет следующую форму:

`phi тип, [значение_1, label метка_1], ..., [значение_N, label метка_N]`, где значения – это временные переменные SSA-формы, хранящие результат исполнения каких-либо инструкций, а метки – узлы CFG, с которых пришло данное значение. Результат исполнения инструкции в SSA располагается на новую уникальную переменную – виртуальный регистр. Таким образом, входные параметры ф-инструкции всегда являются регистрами, т.е. из памяти не читает. Из определения ф-узла и того факта, что ф-инструкции располагаются в начале узла графа потока управления, следует, что результат сохраняется на виртуальном регистре. **Отсюда заключаем, что ф-инструкция оперирует только с регистрами и не влияет на исследуемый метод статического анализа многопоточных алгоритмов.**

Отдельно стоит уделить внимание инструкциям, которые передают управление в потоке исполнения программы, так называемые инструкции перехода или branch-инструкции. В LLVM IR каждый линейный участок, что есть CFG-узел в графе потока управления, заканчивается соответствующей branch-инструкцией. В LLVM IR существуют следующие branch-инструкции [23]:

- *ret* – инструкция, которая используется для возрата управления из функции в точку вызова функции.

```

ret <type> <value> ; возврат значения из не void функции

ret void ; возврат из void функции

```

- *br* – инструкция, которая используется для передачи управления в другой линейный участок в текущей функции.

```

br i1 <cond>, label <iftrue>, label <iffalse>

br label <dest> ; безусловный переход

```

- *switch* – инструкция, которая используется для передачи управления в один из нескольких линейных участков в зависимости от условия.

```

switch <intty> <value>, label <defaultdest> [ <intty> <val>,

```

```

label <dest> ... ]

```

- *indirectbr* – инструкция, которая реализует непрямой переход к метке внутри текущей функции, причем указан адрес метки, а не имя метки.

```

indirectbr <somety>* <address>, [ label <dest1>, label <dest2>, ... ]

```

- *invoke* – инструкция, которая передает управление указанной функции

```

<result> = invoke [ccconv] [ret attrs] <ptr to function ty>

<function ptr val>(<function args>) [fn attrs]

```

Поскольку происходит, как правило, процедурный анализ кода в процессе поиска RC, то *invoke* или *ret* инструкции не представляют интереса для метода статического анализа, т.к. не приводят к ветвлению управления в CFG процедуры. Также семантика обозначенных выше инструкций показывает, что все инструкции оперируют с метками и адресами на код программы, адреса которых расположены на виртуальных регистрах/переменных SSA-формы.

**Отсюда заключаем, что класс branch-инструкций не влияет на создание неразрешимого состояния гонки, т.к. не оперирует с памятью.** Однако удаление branch-инструкций из анализируемого контекста программы дает основание трансформировать ветвление управления, созданное данными branch-инструкциями, в CFG программы. Здесь возникает отдельная проблема корректного изменения ветвления управления в CFG программы. Данная проблема будет рассмотрена ниже.

Таким образом, анализ показывает, что существует возможность разделять инструкции LLVM IR на те, которые влияют на статический анализ, и те, которые могут быть опущены. Принцип отбора инструкции LLVM IR в зависимости от контекста программы до применения статического анализа позволяет значительно упростить представление программы и, как следствие, упростить граф потока управления.

## **2.4. Получения сокращенного оптимизированного промежуточного представления LLVM – Reduced Opt LLVM IR**

В рамках данной работы был разработан программный комплекс по анализу LLVM IR и получения сокращенного промежуточного представления программы. В качестве технического средства для проведения анализа было выбрано представление LLVM IR в виде CFG в DOT-формате. В данном формате генерируется CFG средствами оптимизирующего компилятора, что является удобным, т.к. такой формат легко визуализировать множеством утилит, которые представляют DOT-формат в графическом виде.

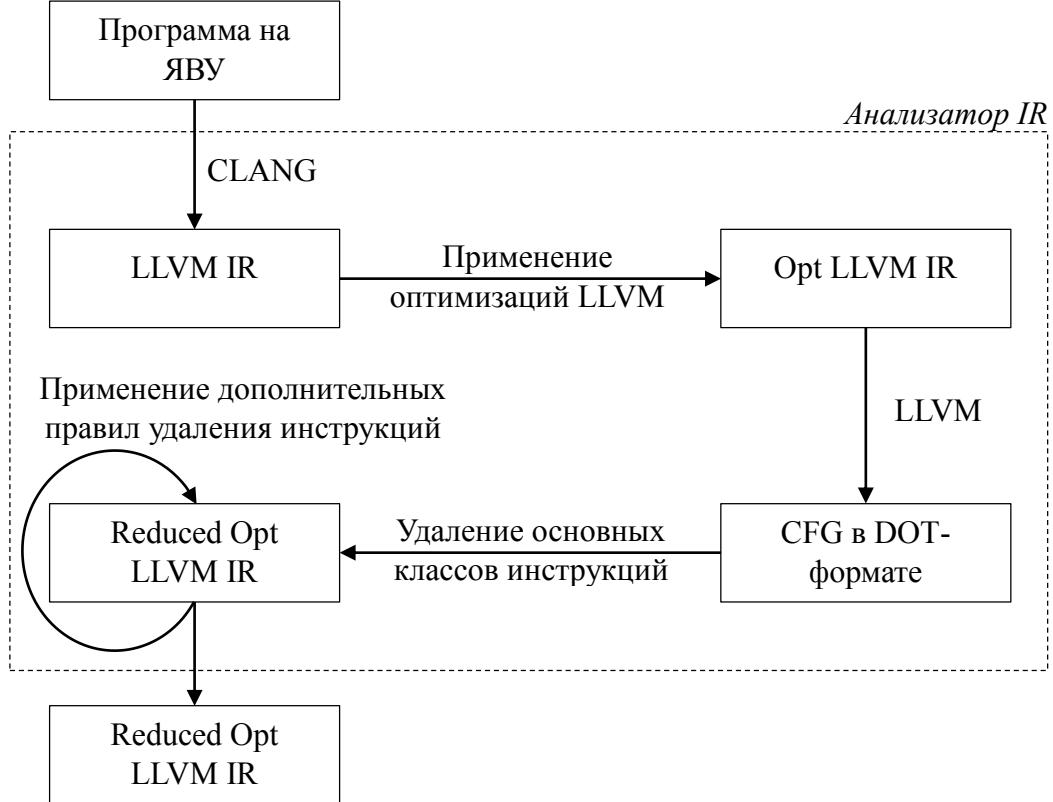

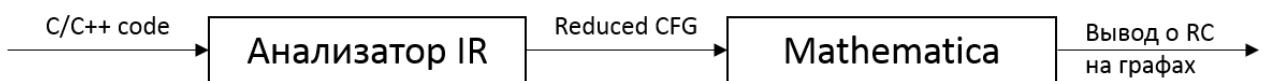

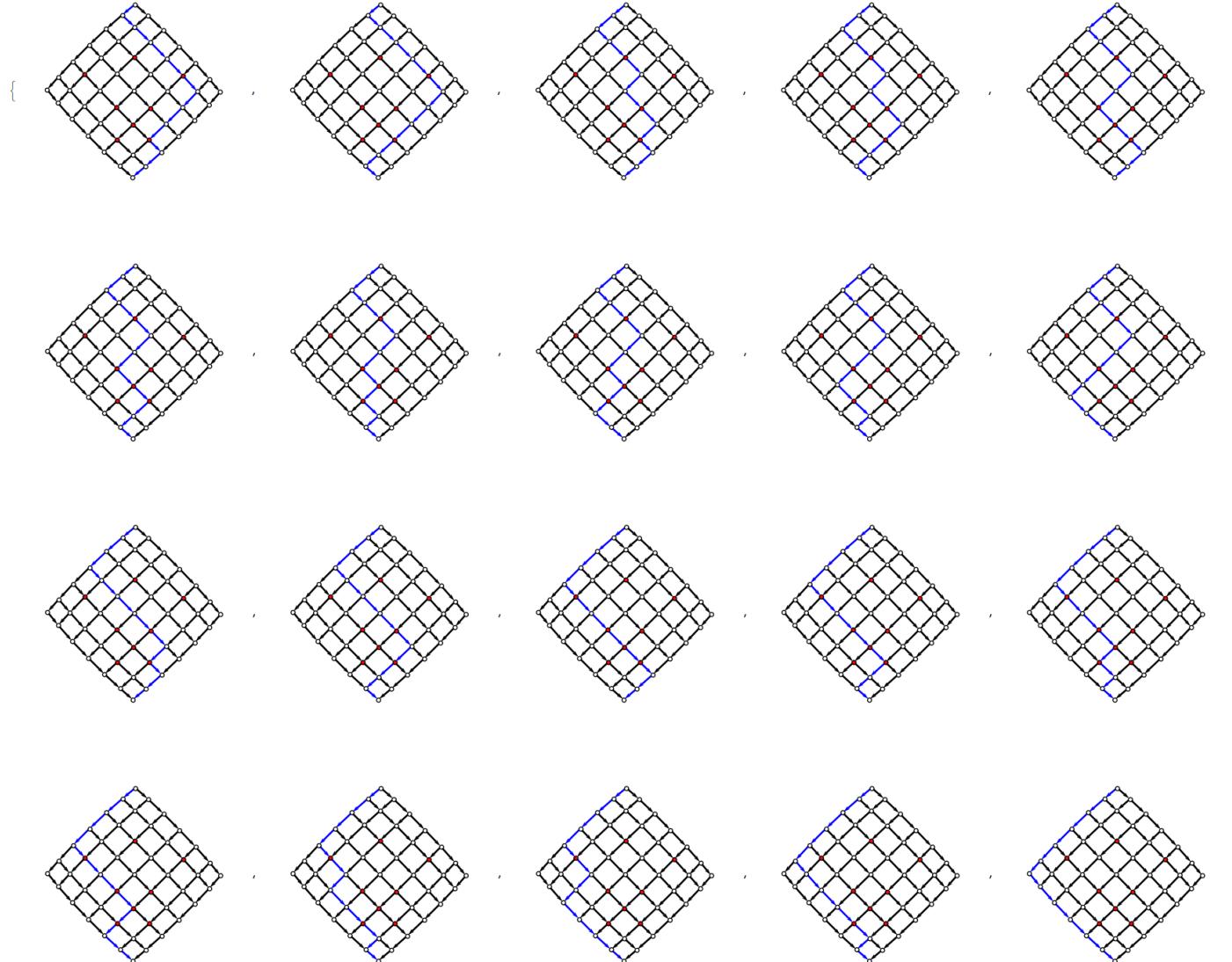

Разработанный программный комплекс для анализа LLVM IR – анализатор IR – состоит из различных этапов преобразования LLVM IR, как в оригинальном виде, так и в DOT-формате. Общая архитектура анализатора изображена на рис. 8. На вход анализатору поступает код программы, написанной на языке высокого уровня (ЯВУ), который средствами front-end компилятора CLANG транслируется в LLVM IR. В качестве front-end системы может выступить любой другой транслятор, который создает корректное платформонезависимое промежуточное представление LLVM IR [8].

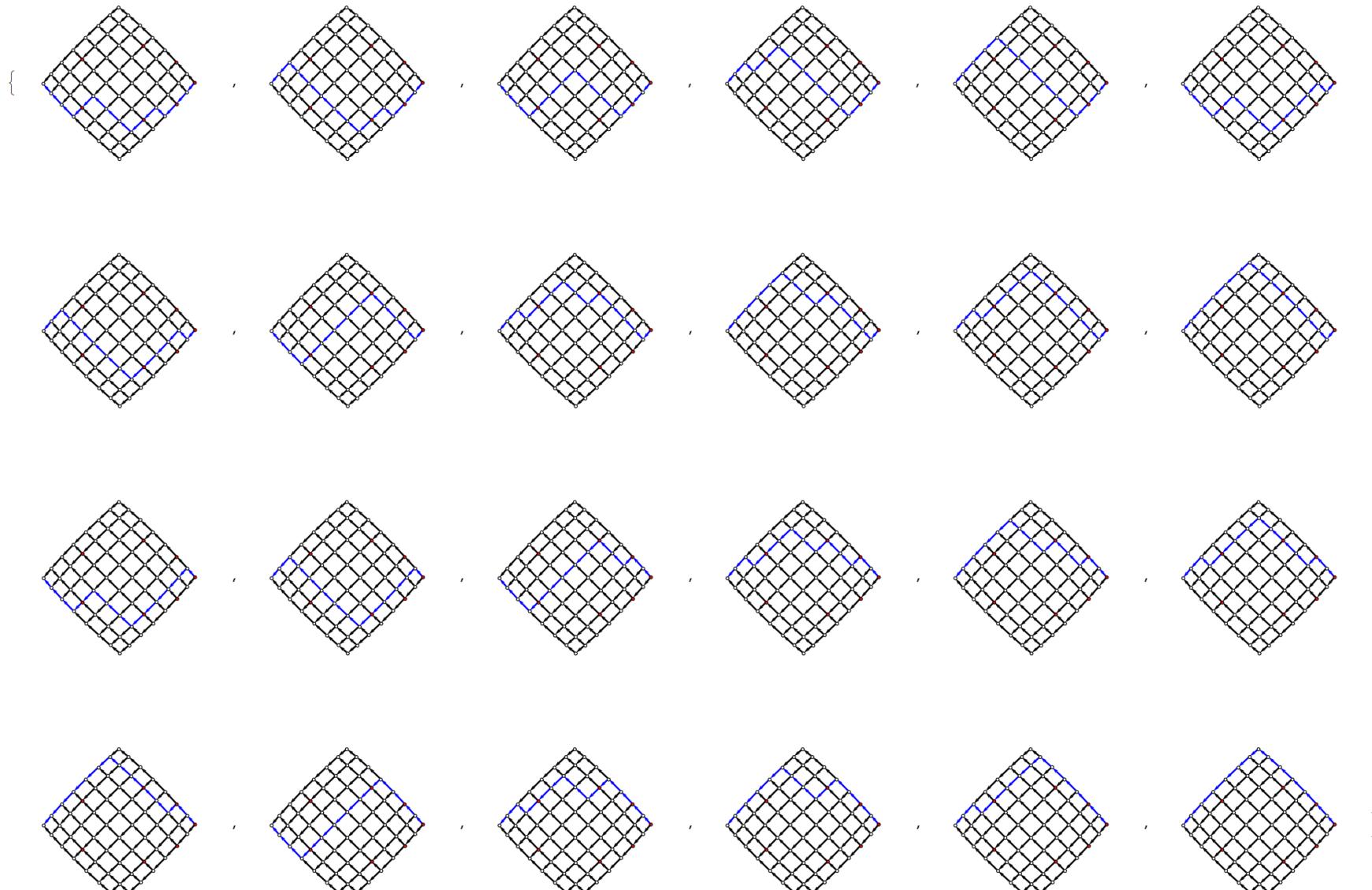

Согласно п. 2.1-2.2 выявленные оптимизации LLVM применяются с целью первичной линеаризации CFG и сокращения общего количества инструкций в программе. В конечном итоге получаем новый вид промежуточного представления LLVM IR – Opt LLVM IR. Далее средствами оптимизирующего компилятора LLVM получаем CFG программы, построенное на LLVM IR, в DOT-формате. Выбор формата представления CFG не является принципиальным и может быть использован любой другой пригодный.

Заключающим этапом в анализаторе является удаление классов инструкций, не влияющих на статический анализ. Вначале удаляются основные классы инструкций, выявленные в рамках данной работы, затем удаляются дополнительные классы инструкций, указанные пользователем.

Рис. 8. Архитектура программного анализатора IR.

Дополнительные классы инструкций необходимы на тот случай, если основных классов инструкций недостаточно, и обнаружены специфические инструкции в LLVM IR, которые не влияют на статический анализ кода.

Согласно п.2.3 было показано, что на статический анализ не влияют инструкции, оперирующие только с виртуальными регистрами или переменными, в том числе branch-инструкции. Таким образом, на линейных участках (CFG-узлах) удаляются инструкции, которые не обращаются к памяти. После этого удаляются дополнительные инструкции из блока дополнительных правил удаления инструкций. В свою очередь к удалению могут быть отнесены инструкции работы с памятью, которая не разделяется между потоками [7].

Надо отметить, что данный этап при удалении branch-инструкций не влечет изменение в структуре линейных участков CFG, т.е. линейные участки не объединяются и не удаляются. Таким образом, структура ветвления управления в CFG сохраняется для последующего этапа анализа графа потока управления.

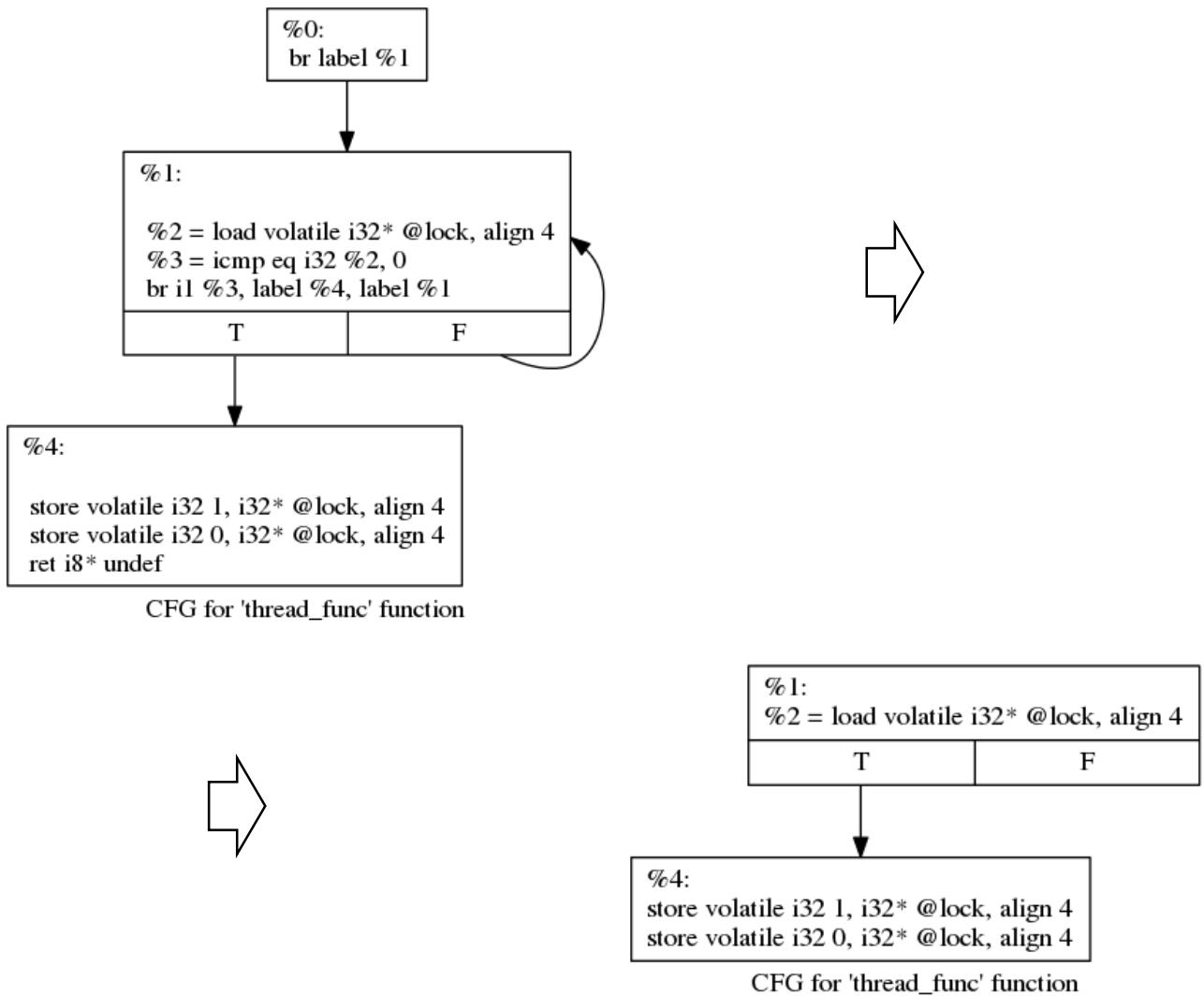

Этап сокращения промежуточного представления очень эффективен в промышленных комплексах программ, где логика каждого потока более нагружена локальным функционалом, не связанным с разделяемыми переменными. Поэтому для наглядности рассмотрим пример получения Reduced Opt IR в алгоритме Петерсона без этапа применения оптимизаций LLVM. Представим, что промежуточное представление первого потока (см. рис. 6) сразу попал на этап получения Reduced Opt IR. Рассмотрим CFG первого потока согласно рис. 6:

```

digraph "CFG for 'thread1_func' function" {

label="CFG for 'thread1_func' function";

Node0x1d27ff0 [shape=record,label="{%0:\l %1 = alloca i8*,\n        align 8\l store i8* %args_ptr, i8** %1, align\n        8\l store volatile i32 1, i32* @turn, align 4\l\n        store volatile i32 1, i32* @flag0, align 4\l br\n        label %2\l}"];

Node0x1d27ff0 -> Node0x1d28280;

Node0x1d28280 [shape=record,label="{%2:\l\l %3 = load\n        volatile i32* @turn, align 4\l %4 = icmp eq i32\n        %3, 1\l br i1 %4, label %5, label\n        %8\l|{<s0>T|<s1>F}\l}"];

Node0x1d28280:s0 -> Node0x1d284c0;

Node0x1d28280:s1 -> Node0x1d28520;

Node0x1d284c0 [shape=record,label="{%5:\l\l %6 = load\n        volatile i32* @flag1, align 4\l %7 = icmp eq\n        i32 %6, 1\l br label %8\l}"];

Node0x1d284c0 -> Node0x1d28520;

Node0x1d28520 [shape=record,label="{%8:\l\l %9 = phi i1 [\n        false, %2 ], [ %7, %5 ]\l br i1 %9, label %10,\n        label %11\l|{<s0>T|<s1>F}\l}"];

Node0x1d28520:s0 -> Node0x1d28910;

Node0x1d28520:s1 -> Node0x1d28970;

```

```

Node0x1d28910 [shape=record,label="%10:\l\l br label

%2\l"];

Node0x1d28910 -> Node0x1d28280;

Node0x1d28970 [shape=record,label="%11:\l\l store volatile

i32 0, i32* @flag0, align 4\l ret i8*

null\l"];

}

```

В данном примере Анализатор IR удалит все инструкции кроме load и store, после чего Reduced Opt IR примет следующий вид:

```

digraph "CFG for 'thread1_func' function" {

label="CFG for 'thread1_func' function";

Node0x1d27ff0 [shape=record,label="%0:\lstore i8* %args_ptr,

i8** %1, align 8\lstore volatile i32 1, i32*

@turn, align 4\lstore volatile i32 1, i32*

@flag0, align 4\l}"];

Node0x1d27ff0 -> Node0x1d28280;

Node0x1d28280 [shape=record,label="%2:\l%3 = load volatile

i32* @turn, align 4\l|{<s0>T|<s1>F}"];

Node0x1d28280:s0 -> Node0x1d284c0;

Node0x1d28280:s1 -> Node0x1d28520;

Node0x1d284c0 [shape=record,label="%5:\l%6 = load volatile

i32* @flag1, align 4\l"];

Node0x1d284c0 -> Node0x1d28520;

Node0x1d28520 [shape=record,label="%8:\l|{<s0>T|<s1>F}"];

Node0x1d28520:s0 -> Node0x1d28910;

Node0x1d28520:s1 -> Node0x1d28970;

Node0x1d28910 [shape=record,label="%10:\l"];

Node0x1d28910 -> Node0x1d28280;

Node0x1d28970 [shape=record,label="%11:\lstore volatile i32

0, i32* @flag0, align 4\l"];

}

```

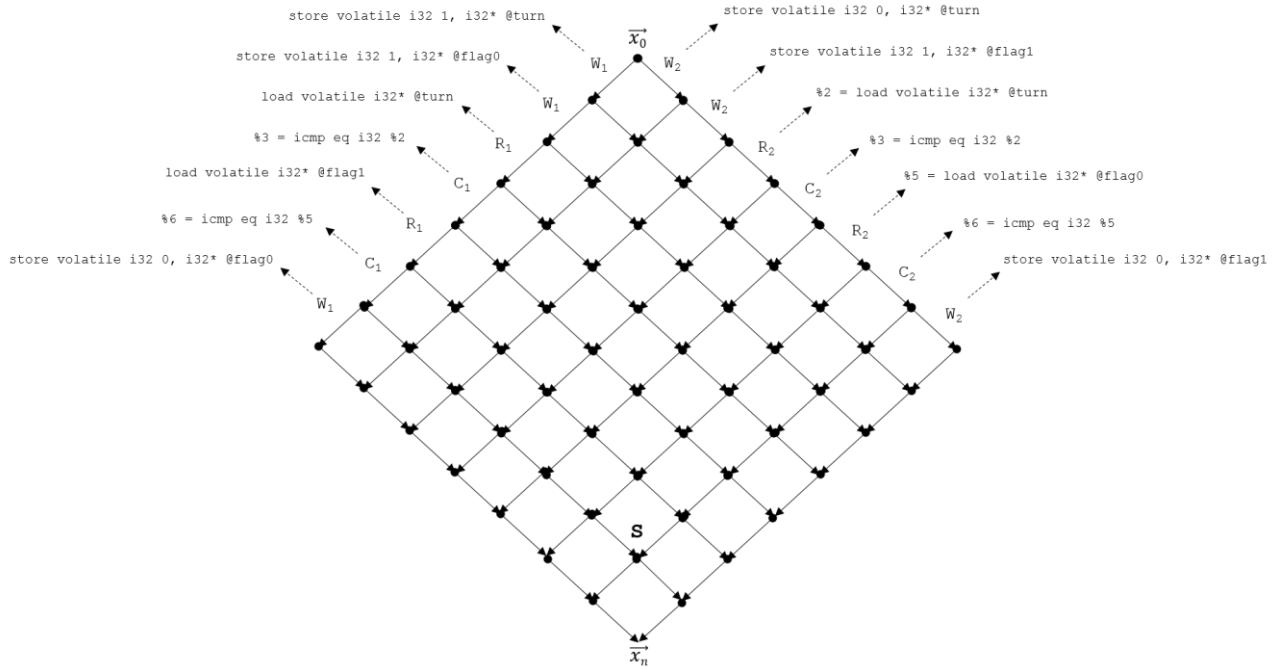

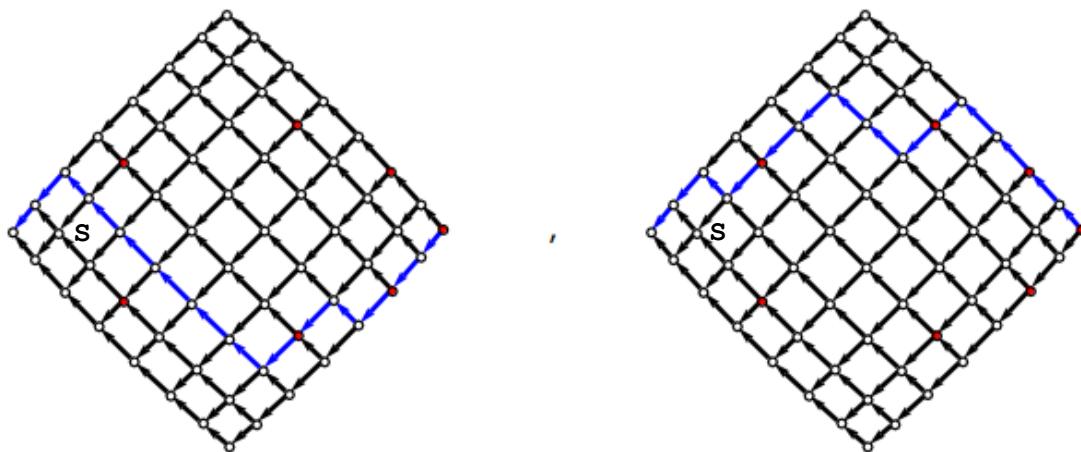

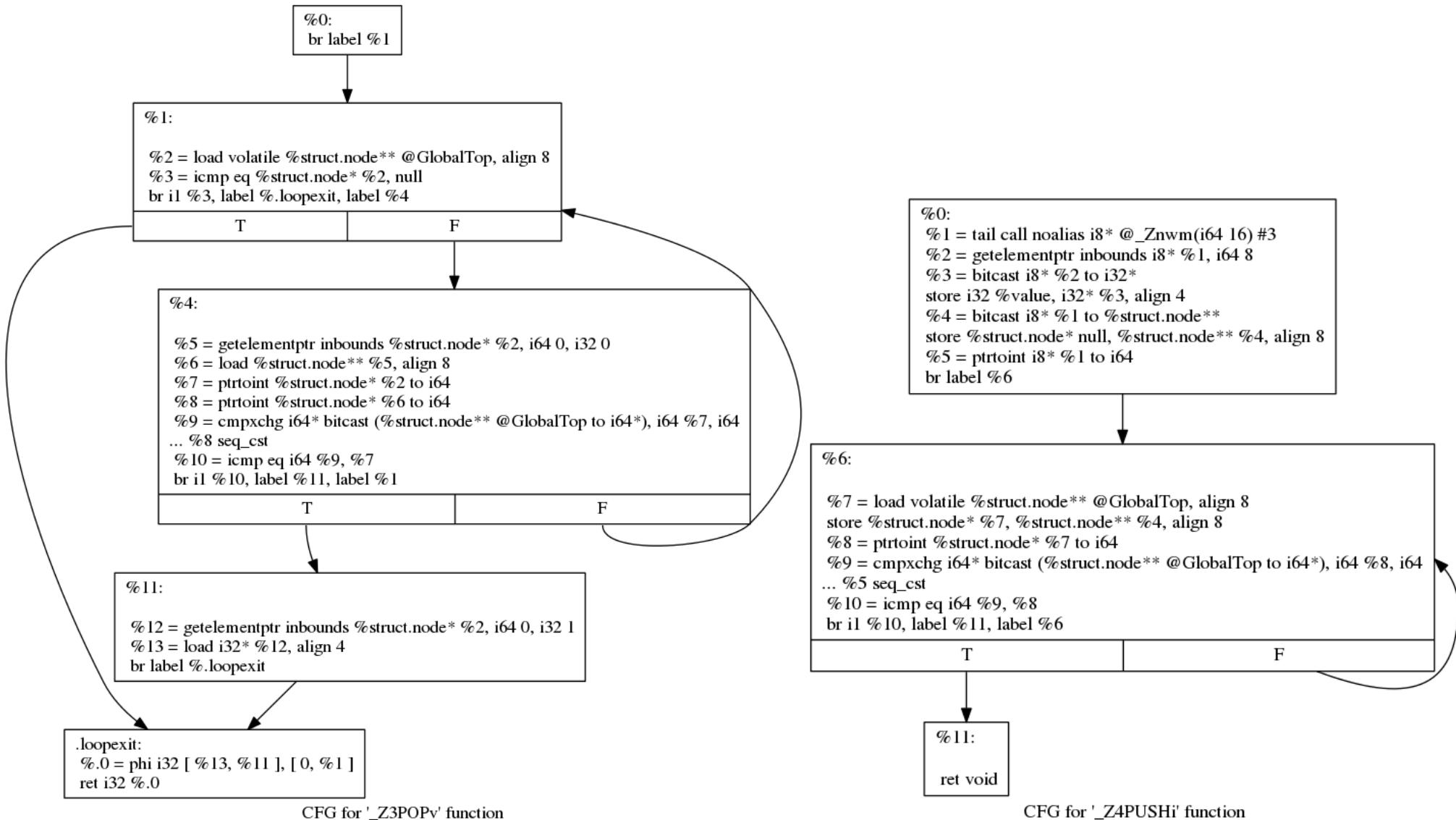

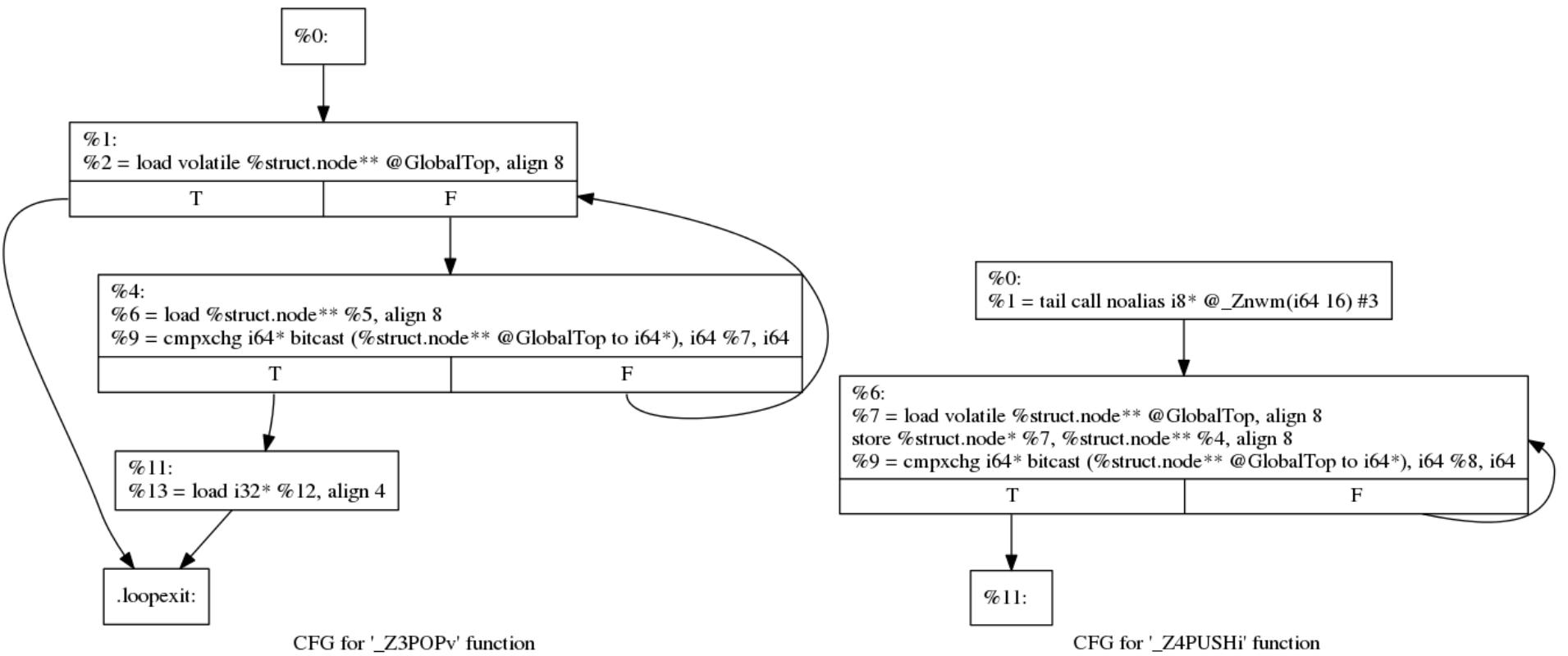

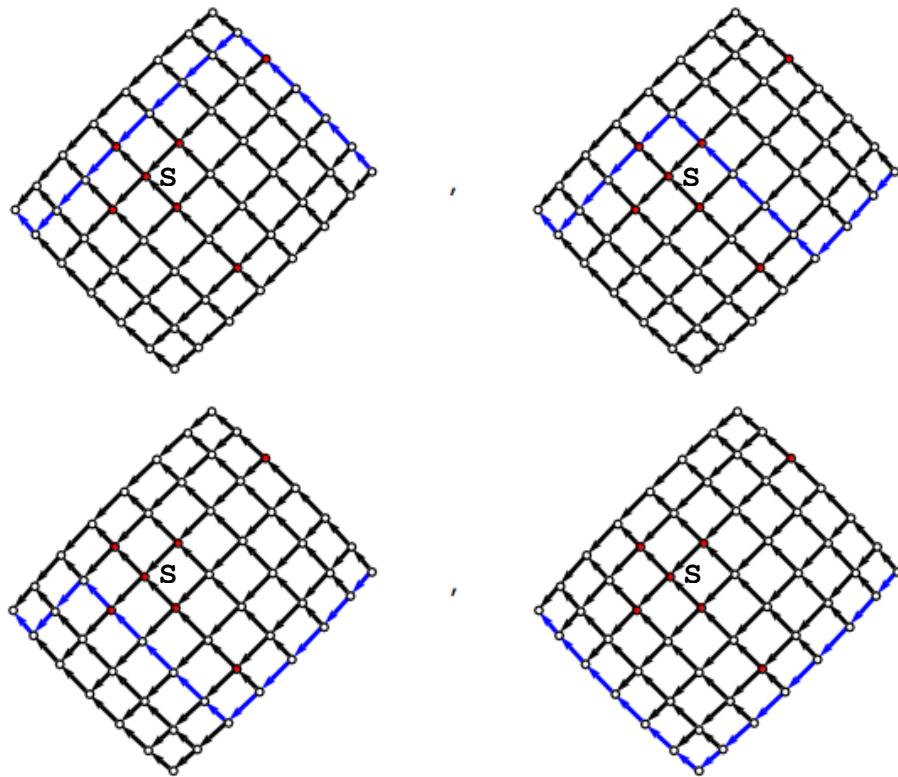

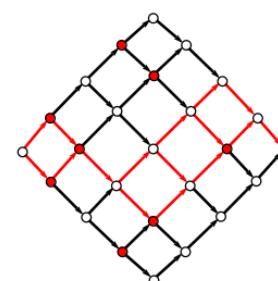

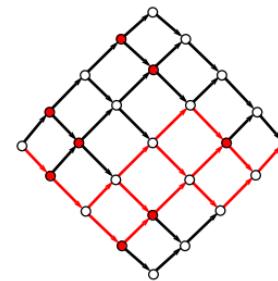

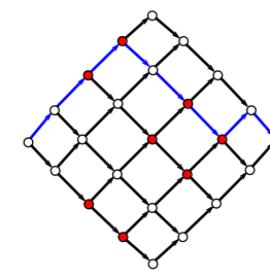

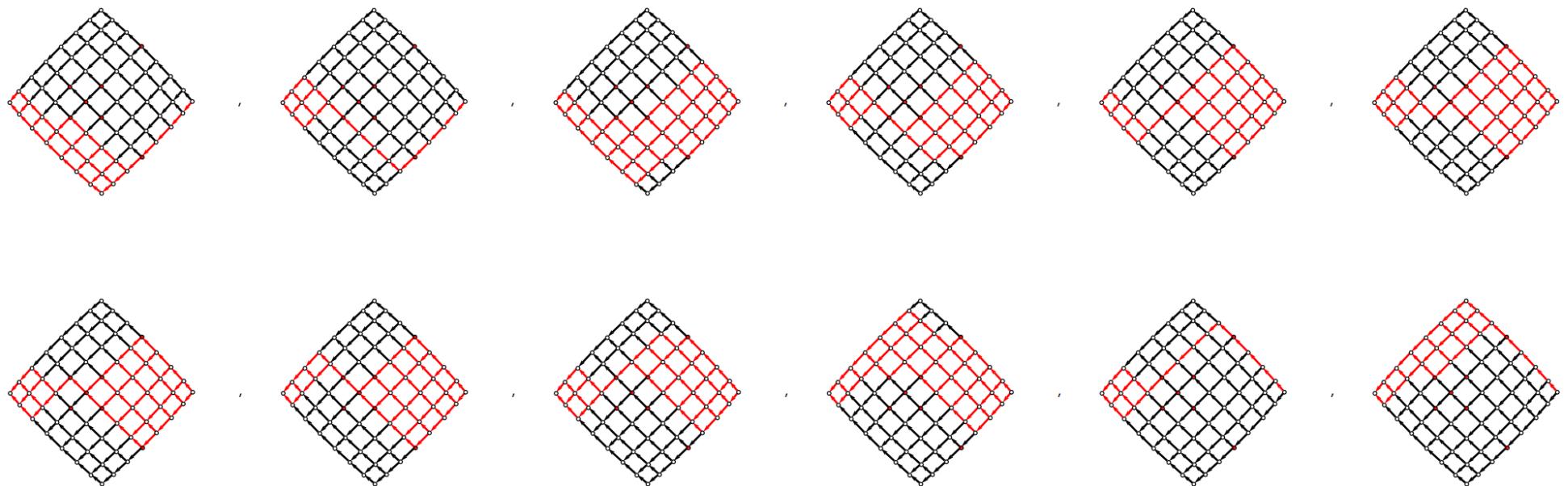

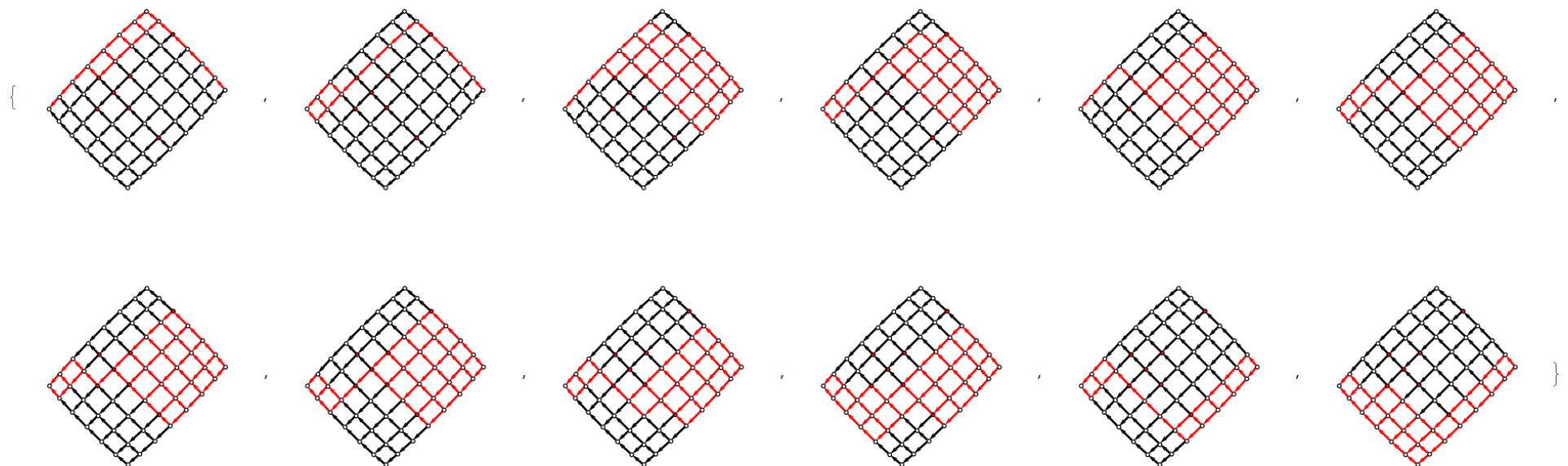

В графическом представлении Reduced Opt IR для алгоритма Петерсона можно увидеть на рис. 9, который получается напрямую из полученного представления после Анализатора IR.

Рис. 9. Визуализация Reduced Opt IR для алгоритма Петерсона.

На рис. 9 видно, что контекст программы существенно упростился. Наблюдается не только сокращение количества инструкций, которые надо было бы анализировать в статическом анализе, но и появляются пустые CFG-узлы, которые дают основание для их удаления и, как следствие, проведения более глубокой линеаризации CFG программы. Процесс линеаризации CFG на подобном контексте программы с учетом соблюдения корректности для статического анализа будет рассмотрен ниже.

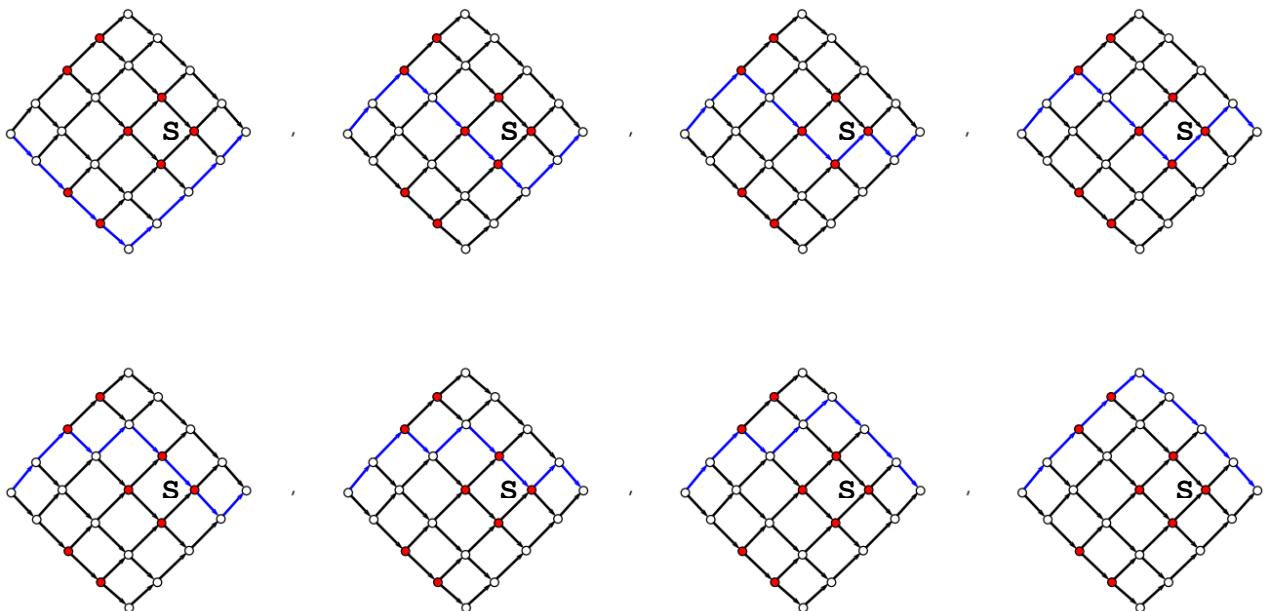

## 2.5. Контекстно-зависимая линеаризация графа потока управления на сокращенном промежуточном представлении программы

Принцип сокращения промежуточного представления программы посредством удаления инструкций, работающих только с регистрами (или виртуальными регистрами в SSA-форме), существенно влияет на представление CFG программы, которое в дальнейшем используется в статическом анализе кода. Инструкции перехода оперируют только с регистрами, поэтому возможна ситуация, когда некоторые узлы CFG остаются пустыми, т.к. в них изначально не было значимых для статического анализа инструкций, таких как load/store инструкции или атомарные инструкции типа CAS. Отсюда заключаем, что **узлы CFG, не содержащие значимых инструкций, являются также незначимые и могут быть удалены из CFG**. При удалении CFG-узла возникает нетривиальная задача – как поступить с входящими и выходящими дугами удаляемого узла. Возникают следующие нетривиальные случаи:

1. Выходящая дуга удаляемого CFG-узла является обратной дугой цикла.

2. Из удаляемого CFG-узла выходят несколько дуг в разные непустые CFG-узлы.